# Department of

# **Electronics & Communiction Engineering**

**QUESTION BANK**

# EC3451 -

## LINEAR INTEGRATED CIRCUITS

**IV SEMESTER**

Regulation – 2021

# MADHA ENGINEERING COLLEGE

DEPT. OF ELECTRONICS & COMMUNICATION ENGG. SEM / YEAR : IV Sem / II Year Branch : E.C.E

EC3451 LINEAR INTEGRATED CIRCUITS

## **SYLLABUS**

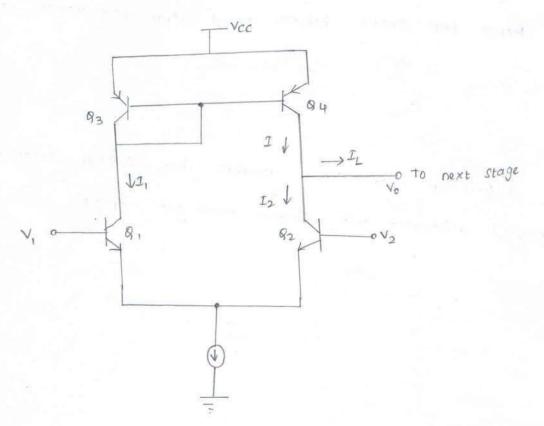

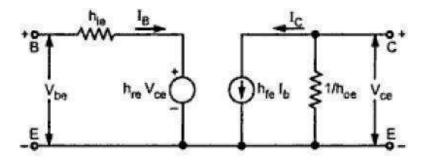

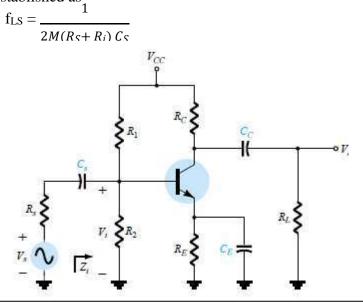

## UNIT I : BASICS OF OPERATIONAL AMPLIFIERS

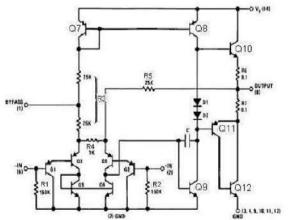

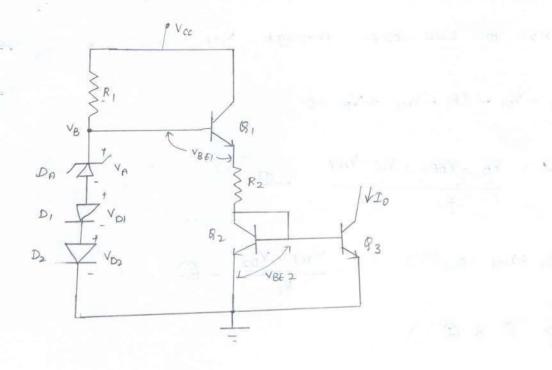

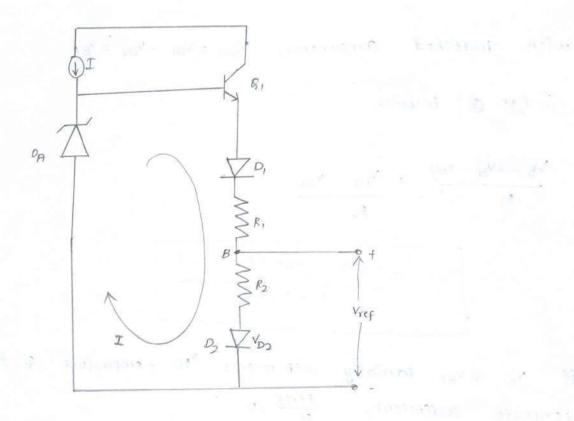

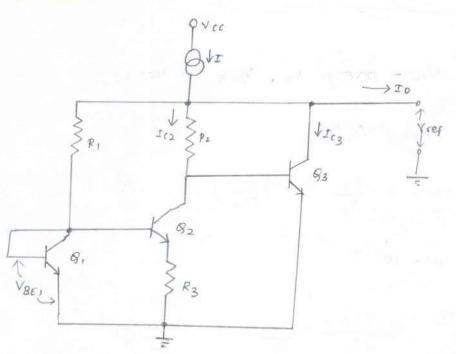

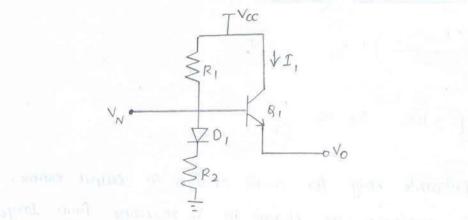

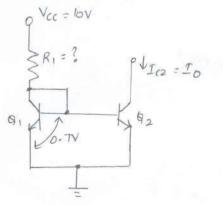

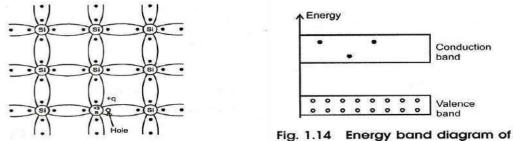

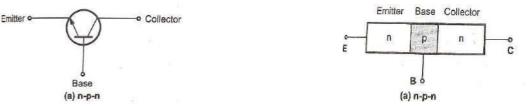

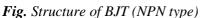

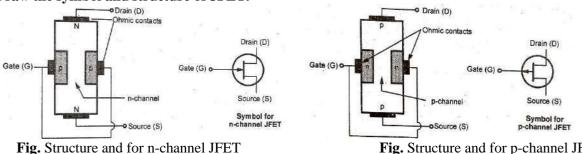

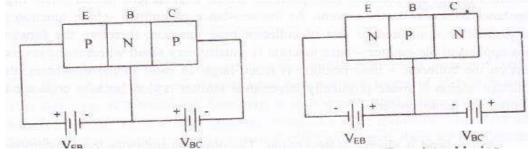

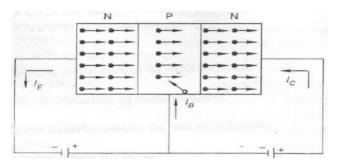

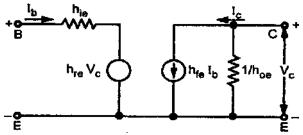

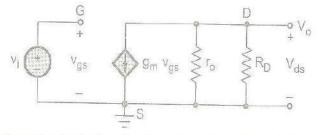

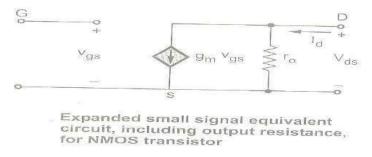

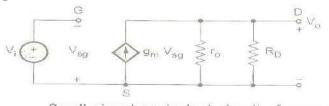

Current mirror and current sources, Current sources as active loads, Voltage sources, Voltage References, BJT Differential amplifier with active loads, Basic information about op-amps – Ideal Operational Amplifier - General operational amplifier stages - and internal circuit diagrams of IC 741, DC and AC performance characteristics, slew rate, Open and closed loop configurations.JFET operational amplifiers-LF155 and TL082

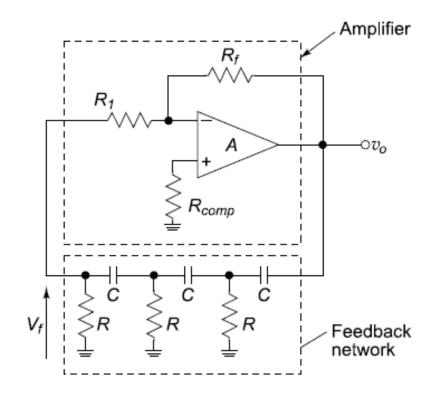

#### UNIT II APPLICATIONS OF OPERATIONAL AMPLIFIERS

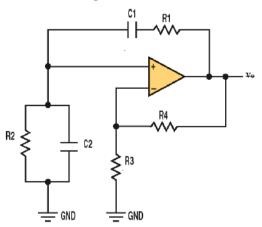

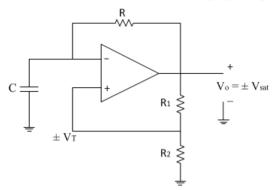

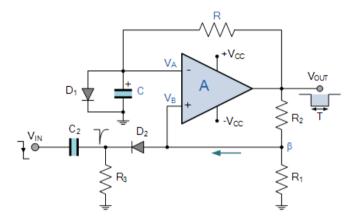

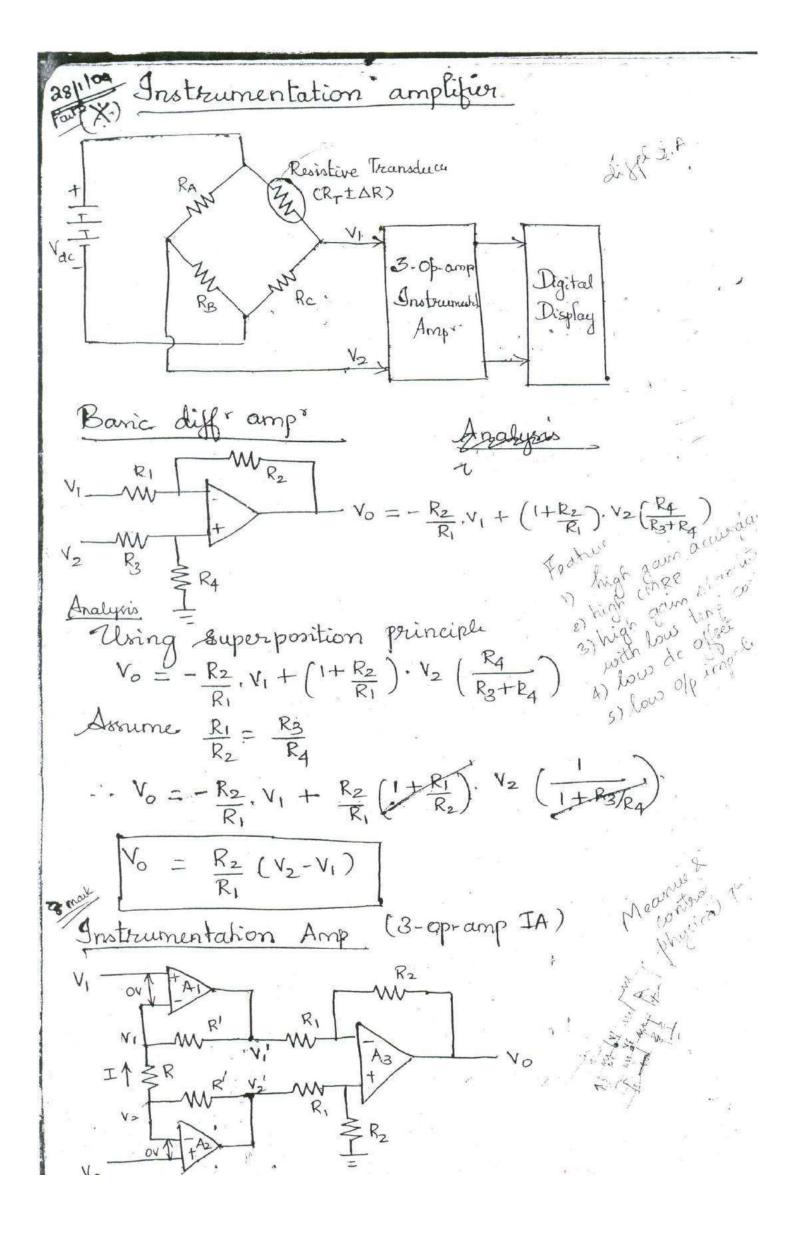

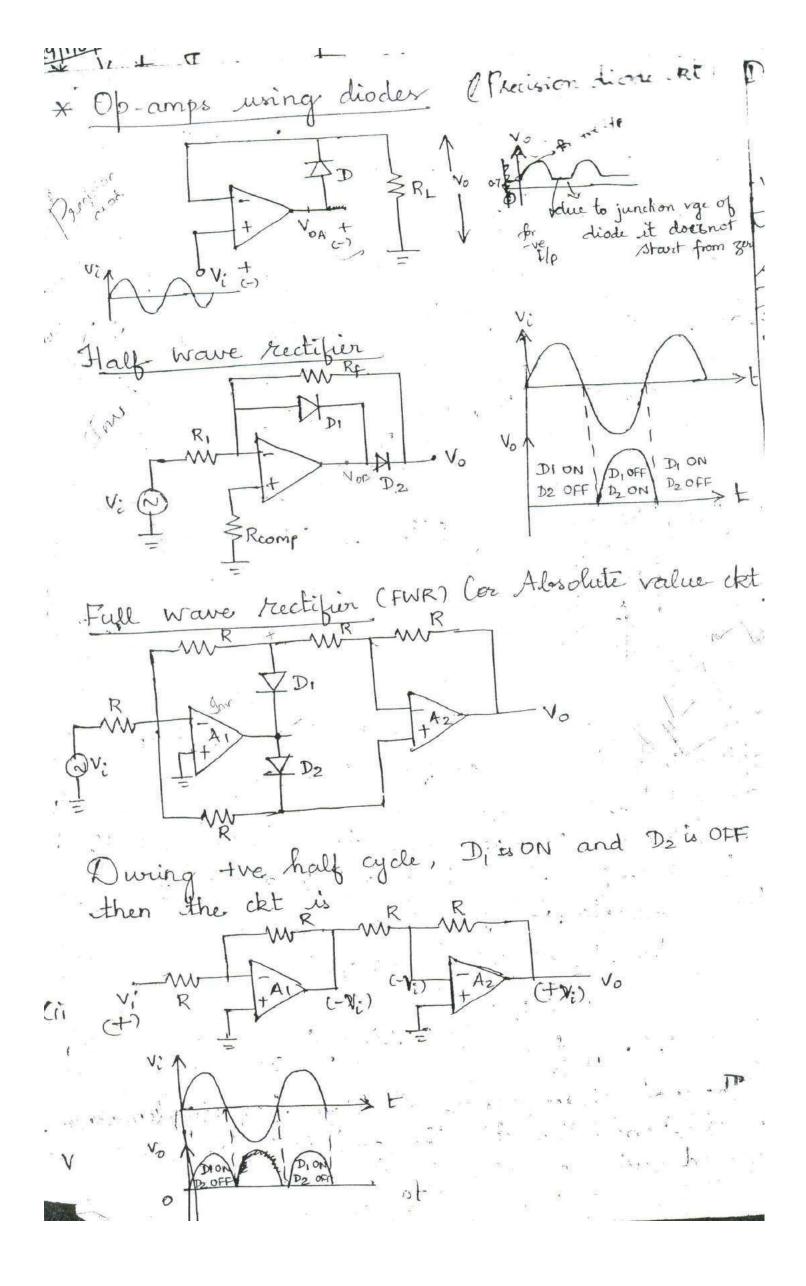

Sign Changer, Scale Changer, Phase Shift Circuits, Voltage Follower, V-to-I and I-to-V converters, adder, subtractor, Instrumentation amplifier, Integrator, Differentiator, Logarithmic amplifier, Antilogarithmic amplifier, Comparators, Schmitt trigger, Precision rectifier, peak detector, clipper and clamper, Low-pass, high-pass and band-pass Butterworth filters.

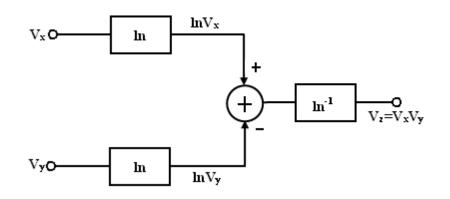

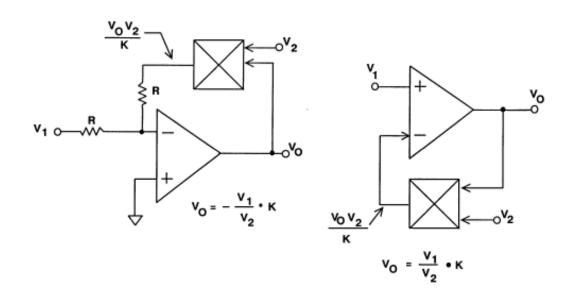

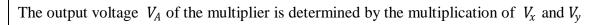

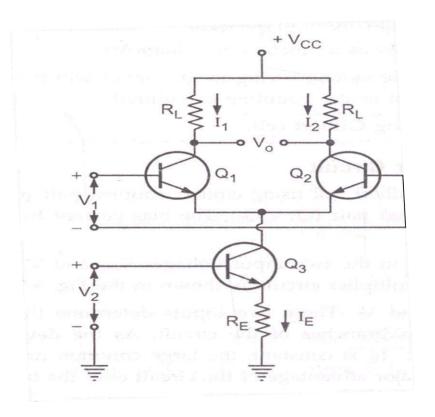

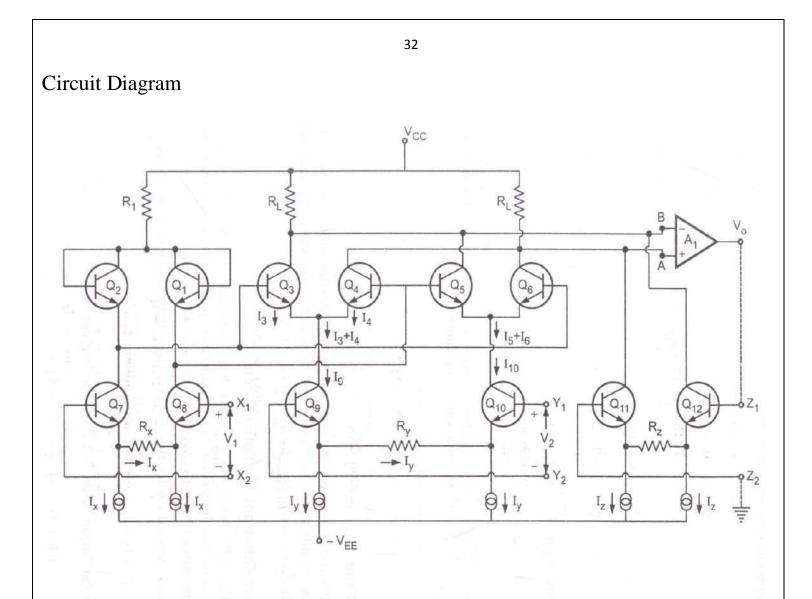

#### UNIT III ANALOG MULTIPLIER AND PLL

Analog Multiplier using Emitter Coupled Transistor Pair - Gilbert Multiplier cell – Variable transconductance technique, analog multiplier ICs and their applications, Operation of the basic PLL, Closed loop analysis, Voltage controlled oscillator, Monolithic PLL IC 565, application of PLL for AM detection, FM detection, FSK modulation and demodulation and Frequency synthesizing and clock synchronization.

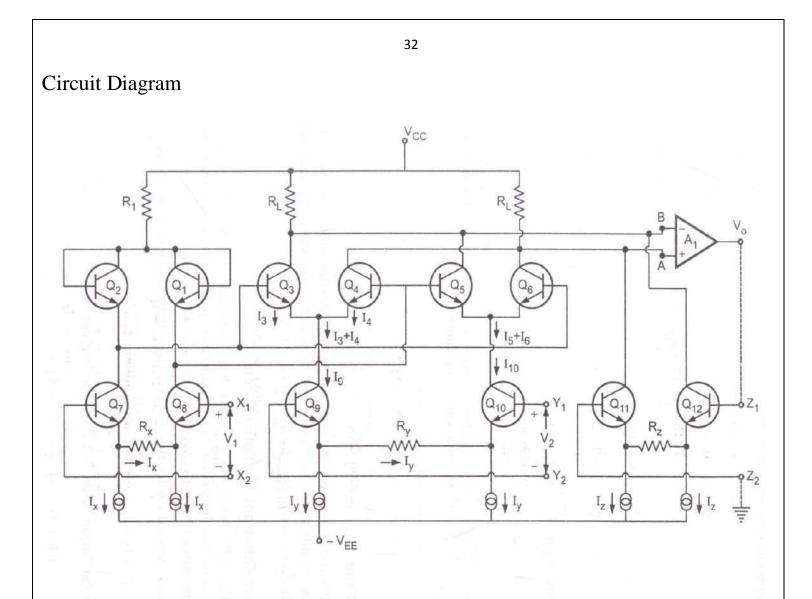

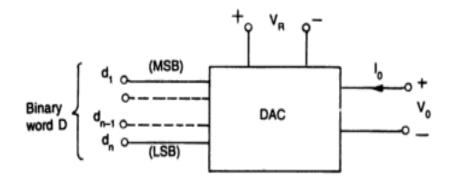

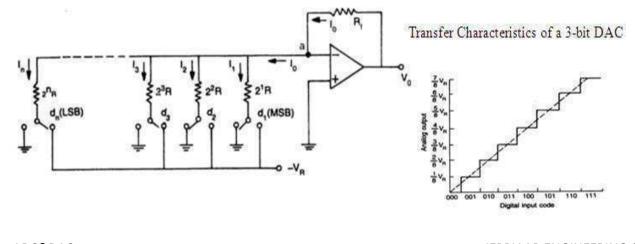

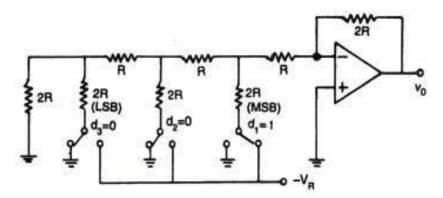

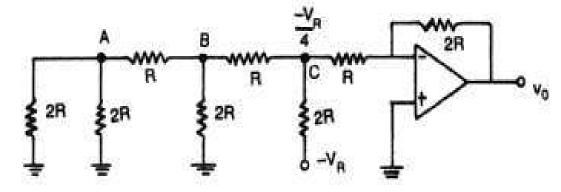

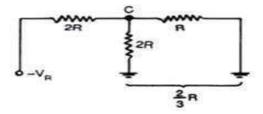

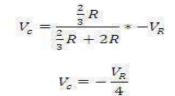

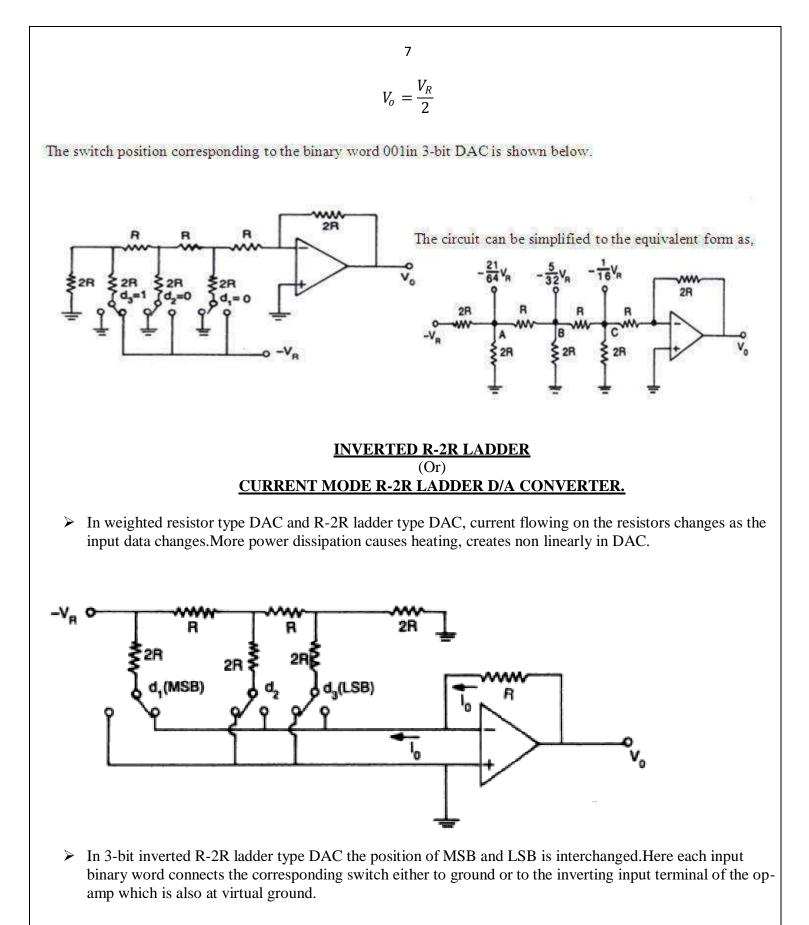

## UNIT IV ANALOG TO DIGITAL AND DIGITAL TO ANALOG CONVERTERS

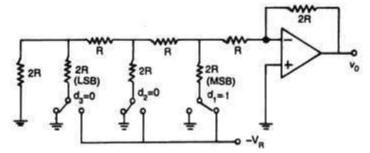

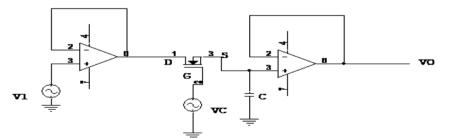

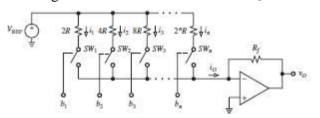

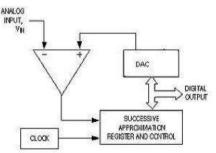

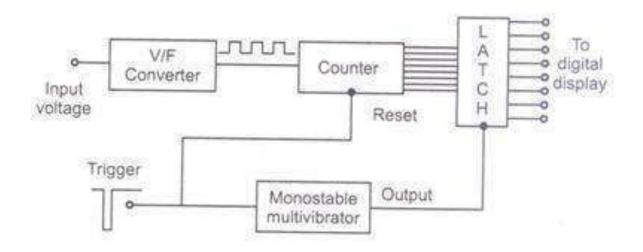

Analog and Digital Data Conversions, D/A converter – specifications - weighted resistor type, R-2R Ladder type, Voltage Mode and Current-Mode R-2R Ladder types - switches for D/A converters, high speed sample-and-hold circuits, A/D Converters – specifications - Flash type - Successive Approximation type - Single Slope type – Dual Slope type - A/D Converter using Voltage-to-Time Conversion - Over-sampling A/D Converters, sigma-delta converters.

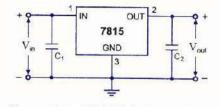

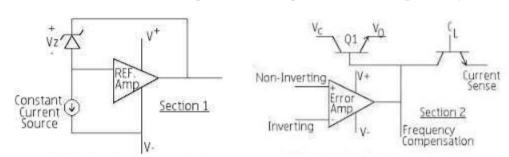

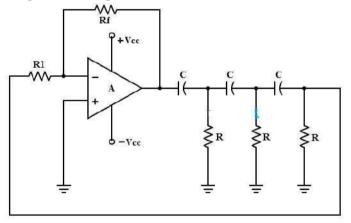

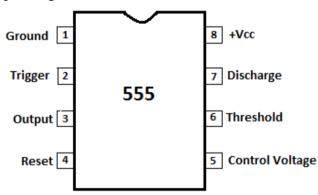

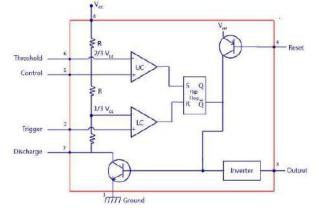

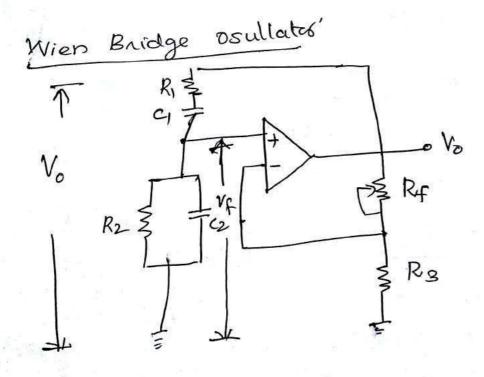

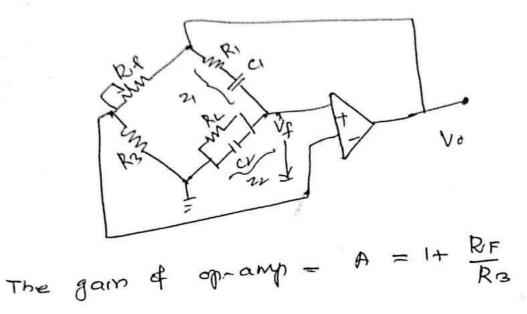

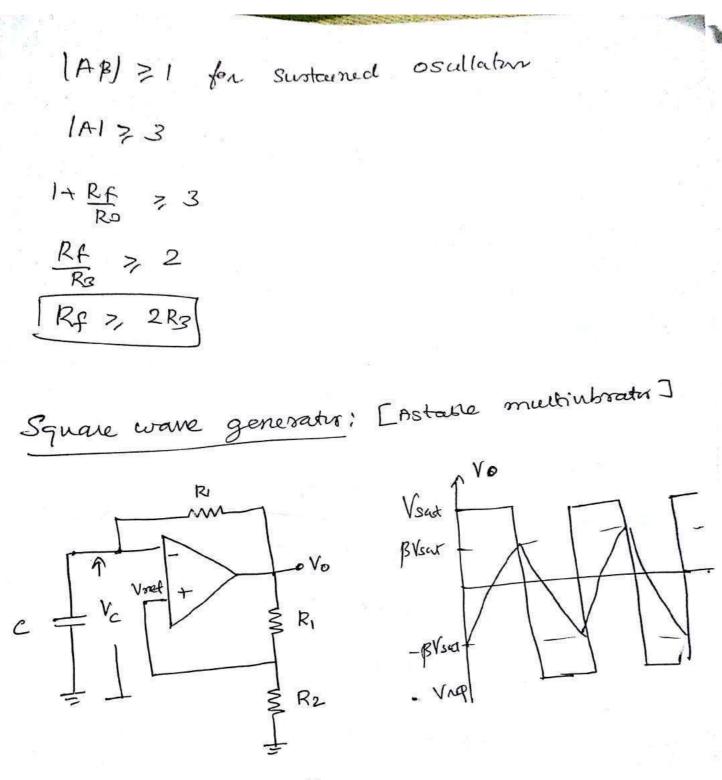

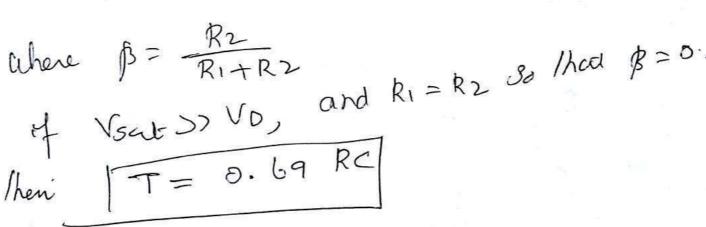

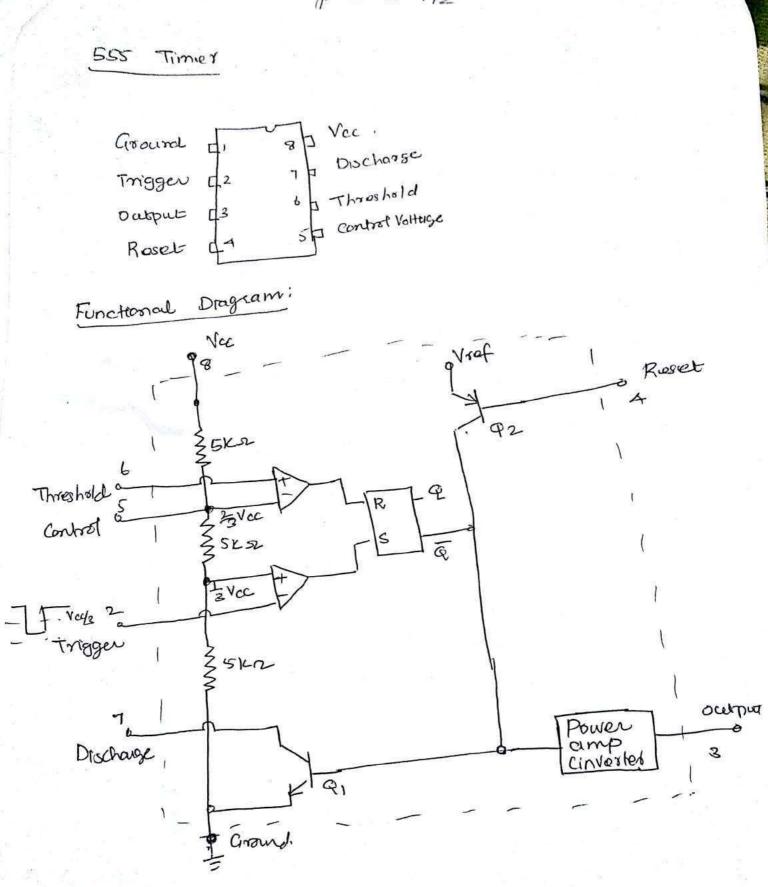

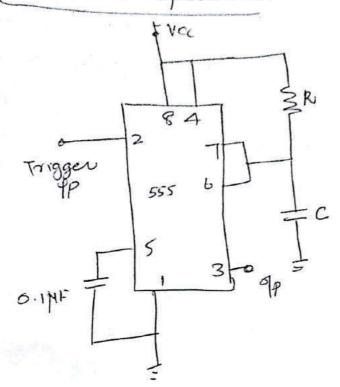

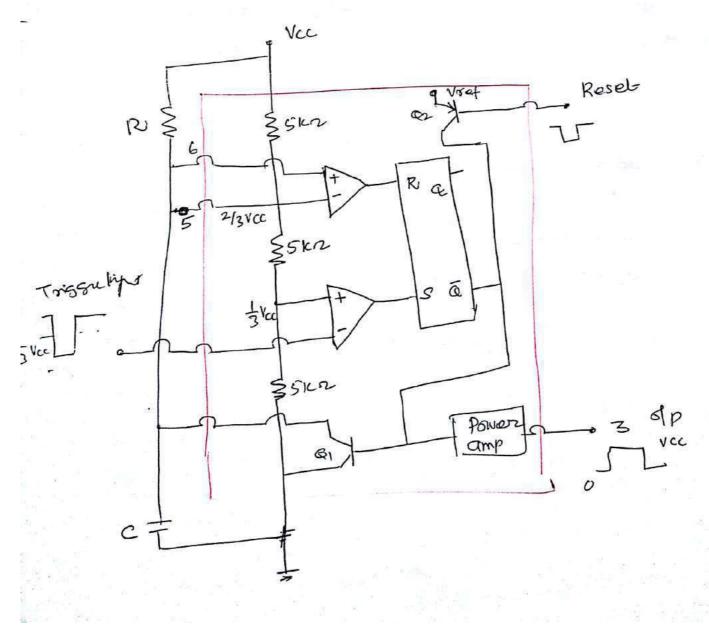

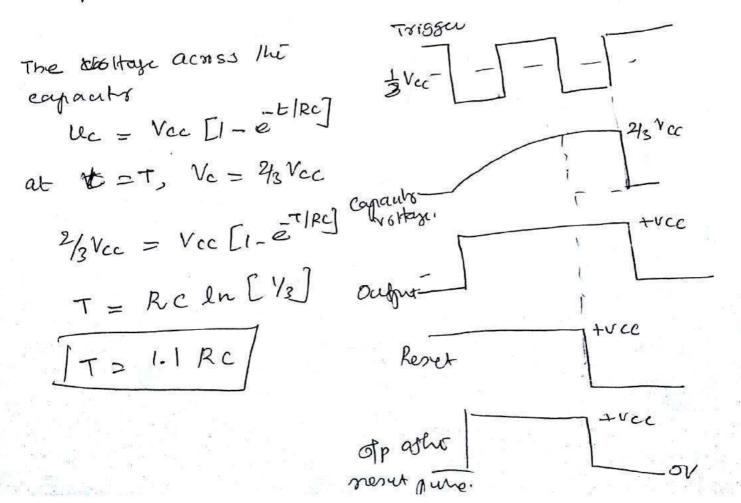

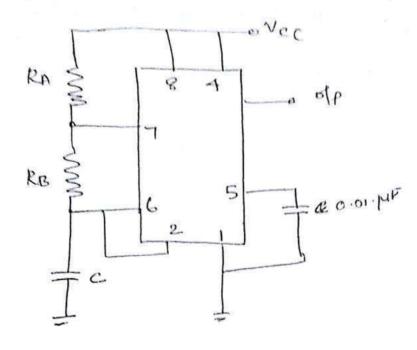

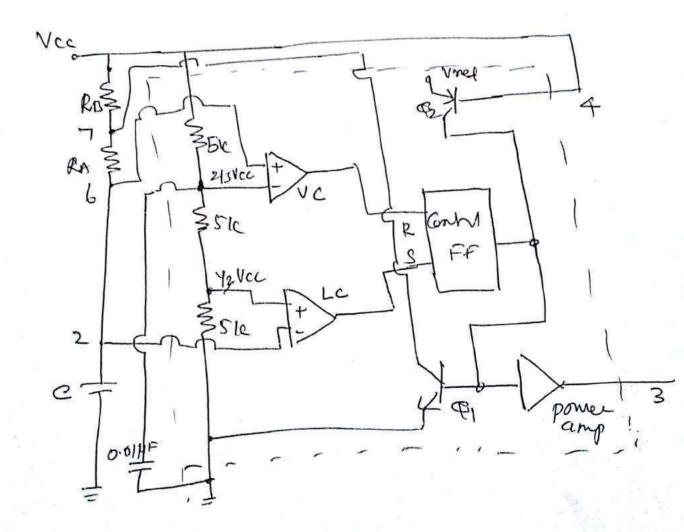

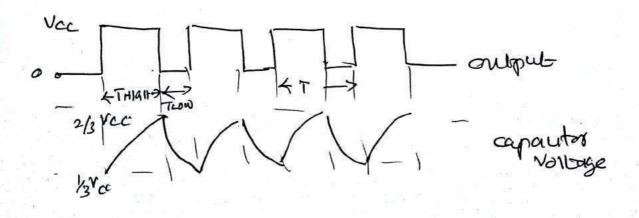

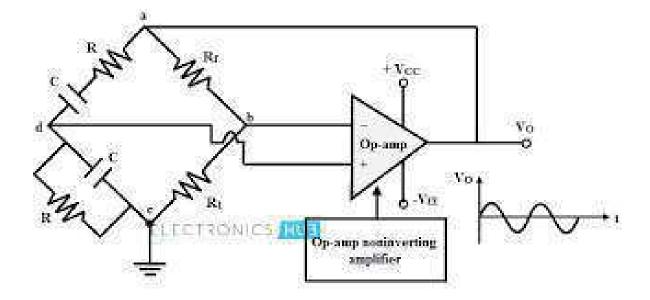

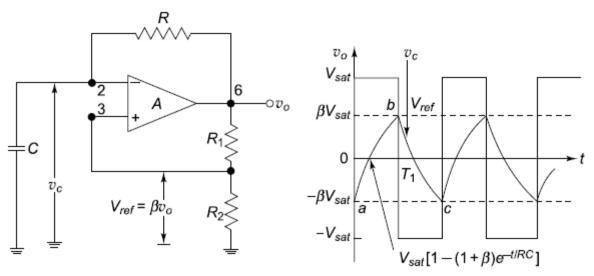

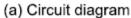

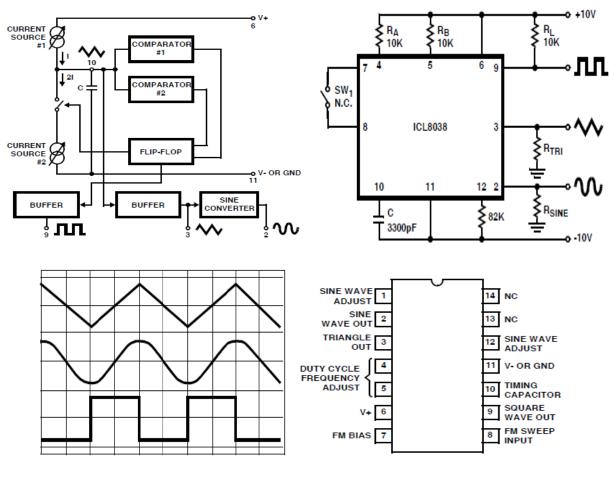

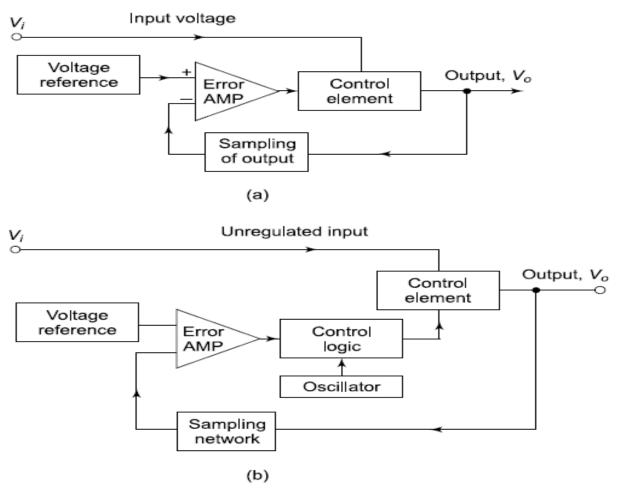

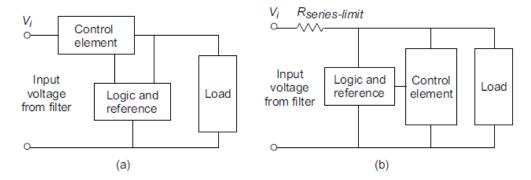

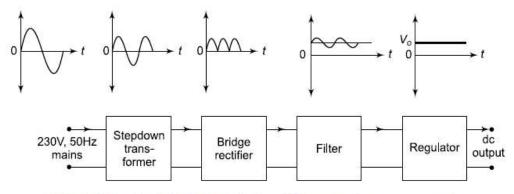

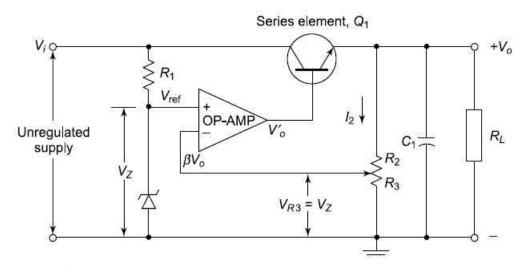

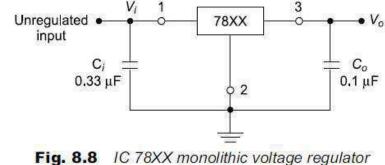

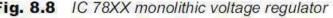

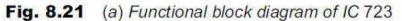

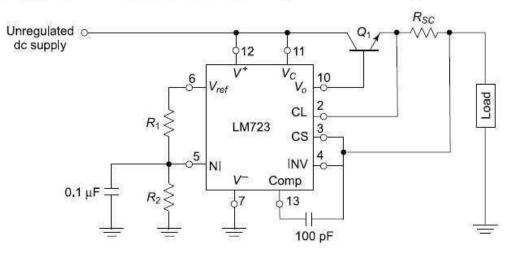

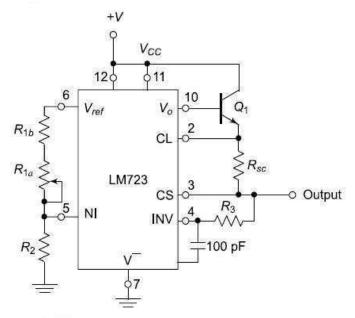

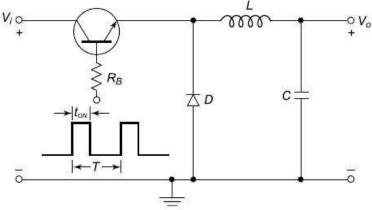

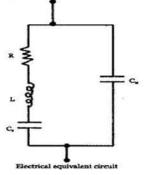

#### UNIT V WAVEFORM GENERATORS AND SPECIAL FUNCTION ICS

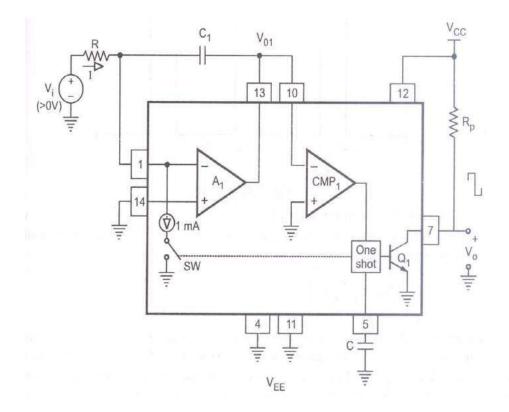

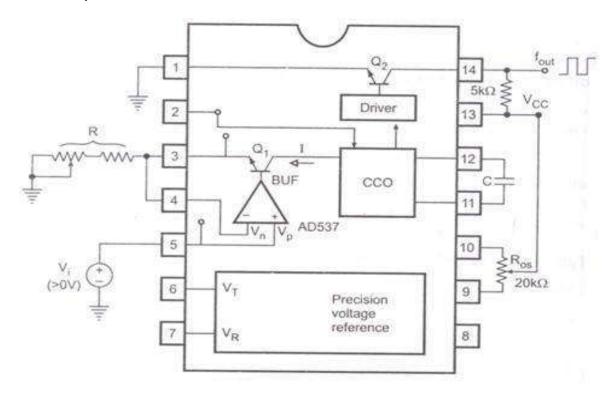

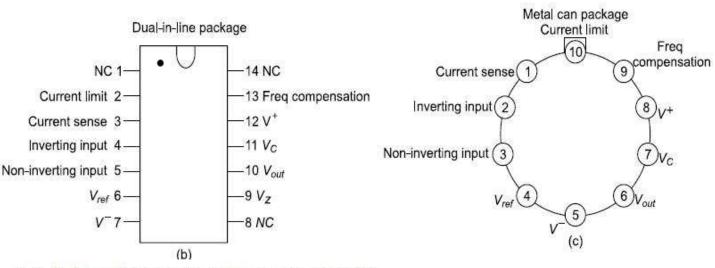

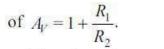

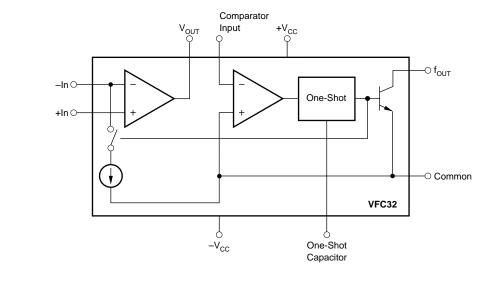

Sine-wave generators, Multivibrators and Triangular wave generator, Saw-tooth wave generator, ICL8038 function generator, Timer IC 555, IC Voltage regulators – Three terminal fixed and adjustable voltage regulators - IC 723 general purpose regulator - Monolithic switching regulator,LowDrop-Out(LDO) Regulators- Switched capacitor filter IC MF10, Frequency to Voltage and Voltage to Frequency converters, Audio Power amplifier, Video Amplifier, Isolation Amplifier, Opto-couplers and fibre optic IC.

#### **TEXT BOOKS:**

D.Roy Choudhry, Shail Jain, "Linear Integrated Circuits", New Age International Pvt. Ltd., 2018.

Sergio Franco, "Design with Operational Amplifiers and Analog Integrated Circuits", 4th Edition, Tata Mc Graw-Hill, 2007.

#### **REFERENCES:**

1. Ramakant A. Gayakwad, "OP-AMP and Linear ICs", 4th Edition, Prentice Hall / Pearson Edu, 2015.

2. Robert F.Coughlin, Frederick F.Driscoll, "Operational Amplifiers and Linear Integrated Circuits", Sixth Edition, PHI, 2001.

3. B.S.Sonde, "System design using Integrated Circuits", 2nd Edition, New Age Pub, 2001

4. Gray and Meyer, "Analysis and Design of Analog Integrated Circuits", Wiley International, 2009.

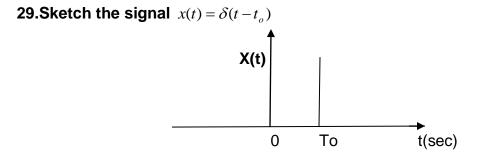

5. William D.Stanley, "Operational Amplifiers with Linear Integrated Circuits", Pearson Education, 2004.

6. S.Salivahanan & V.S. Kanchana Bhaskaran, "Linear Integrated Circuits", TMH, 2016.

9

9

9

9

9

## UNIT-I BASICS OF OPERATIONAL AMPLIFIERS PART-A

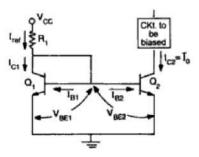

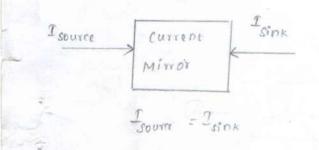

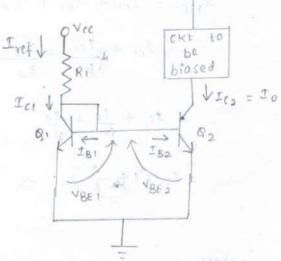

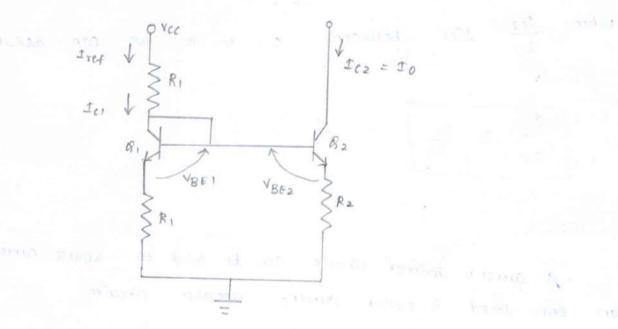

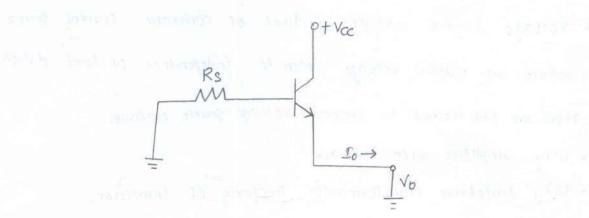

1. State the significance of current mirror circuit

A current mirror circuit is designed to copy a current through one active device by controlling the current in another active device of a circuit keeping the output current constant regardless of loading. The current mirrors are used to provide bias currents and active loads to circuits

- 2. Mention the application of LF155

- Precision high speed integrators

- Fast D/A and A/D converters

- High impedance buffers

- Wideband low noise low drift amplifiers

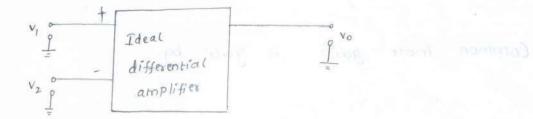

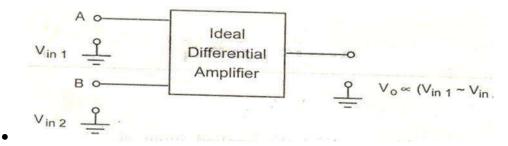

- 3. Define differential mode gain

# It is the change in the difference between the two outputs divided by the change in the difference between the two inputs.

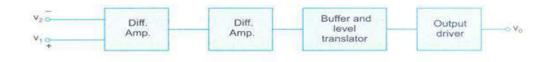

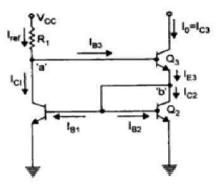

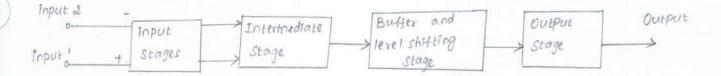

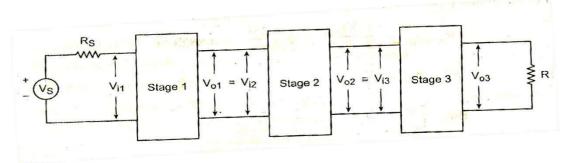

Enumerate any two blocks associated with op-amp schematic. [April/May 2018]

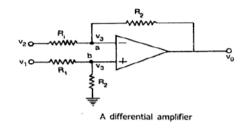

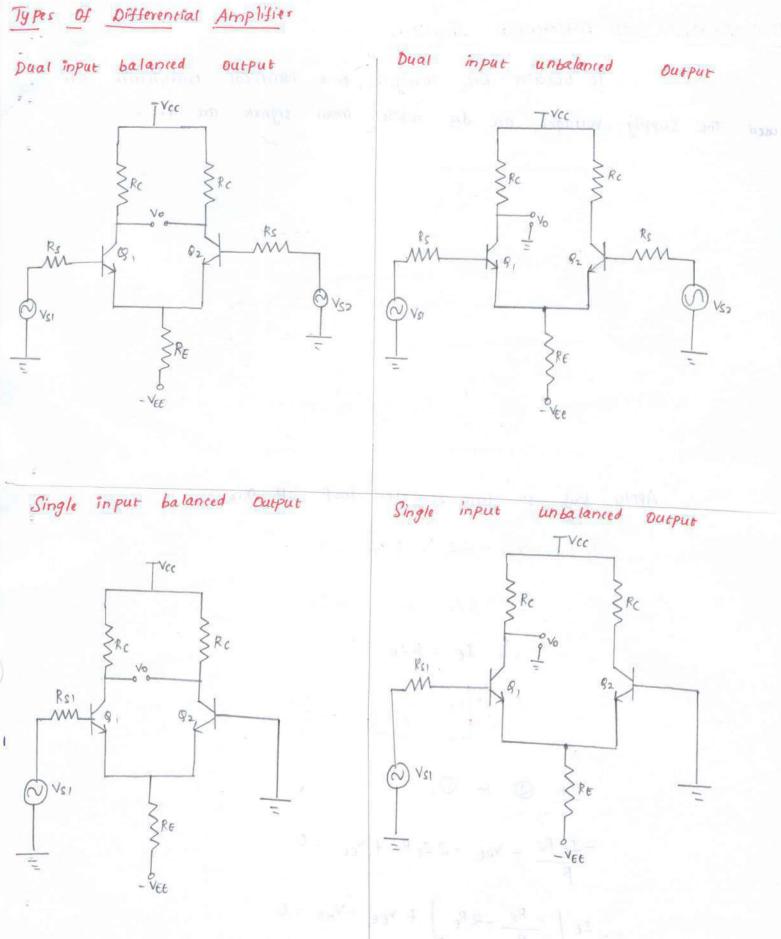

Differential amplifier

Differential amplifier is to provide high gain to difference mode signal and cancel the common mode signal.

## Level translator

As the op-amp is used to operate down to d.c no coupling capacitor is used. Because of direct coupling ,the d.c level rises from stage to stage. This increase in d.c level tends to shift the operating point of the next stage. This in turn limits the output swing and may distort the output signal. Therefore it becomes essential that the quiescent voltage of one stage is shifted before it is applied to the next stage.

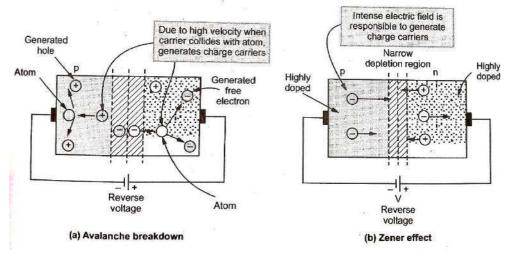

- 5. What are the two methods can be used to produce voltage sources? [April/May 2018]

- Using temperature compensation

- Using avalanche diode.

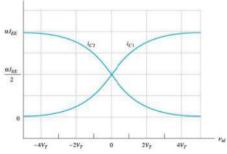

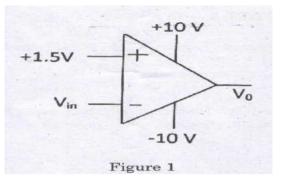

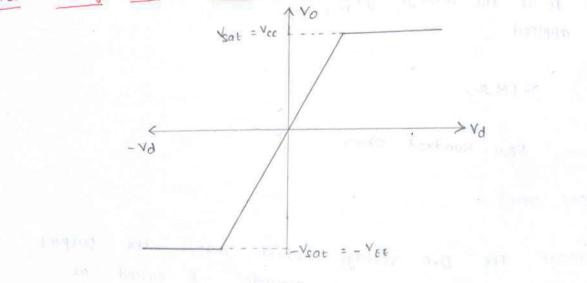

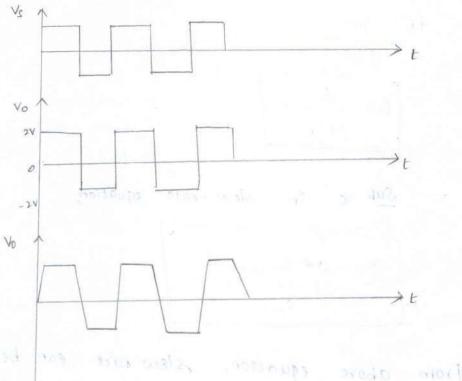

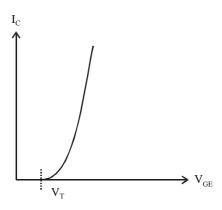

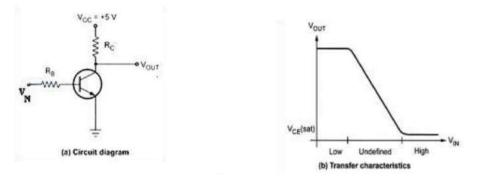

- 6. Draw the dc transfer characteristics of a BJT differential amplifier and define differential mode input voltage [Nov/Dec 2017]

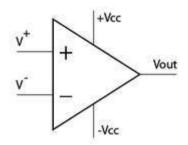

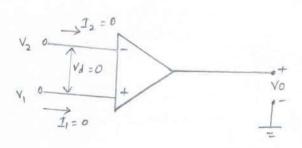

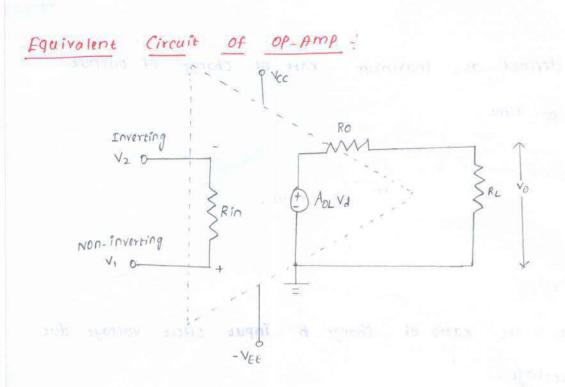

7. Write down the characteristics of ideal operational amplifier? [Nov/Dec 2018]

[April/May 2017][April/May 16]

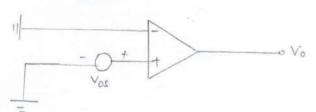

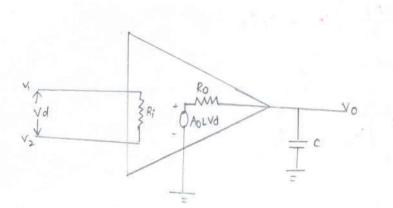

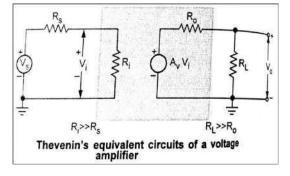

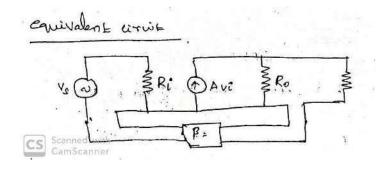

Open loop voltage gain,  $(AOL) = \infty$ Input impedance  $(Ri) = \infty$ Output impedance (Ro) = 0Bandwidth  $(BW) = \infty$ Zero offset Vo = 0, when V1 = V2 = 0

## [April/May 2019]

[Nov/Dec 2018]

[April/May 2019]

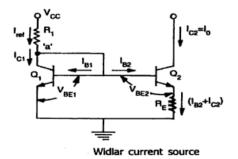

8. Why is the current mirror circuit used in differential amplifier stages? [April/May 2017]

The current mirror is a special case of constant current bias and the current mirror bias requires of constant current bias and therefore can be used to set up currents in differential amplifier stages

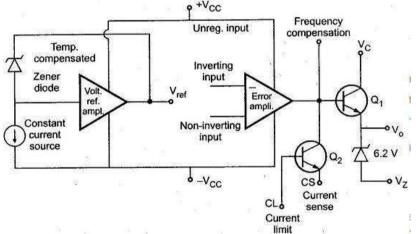

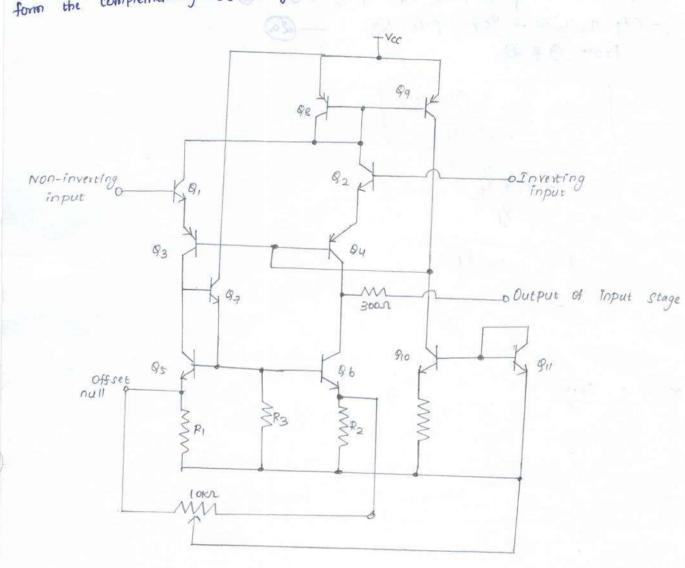

9. Draw the Internal Block diagram of Op – Amp (IC 741) [Nov/Dec 2016]

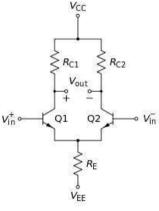

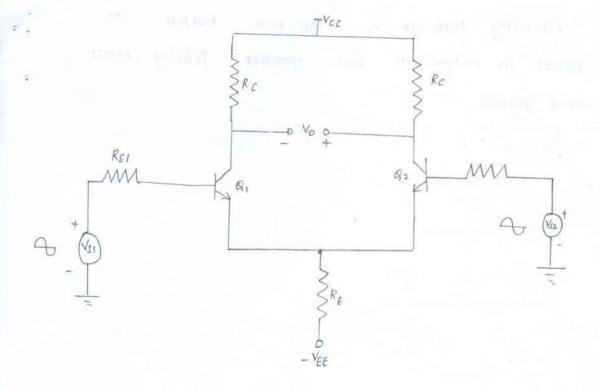

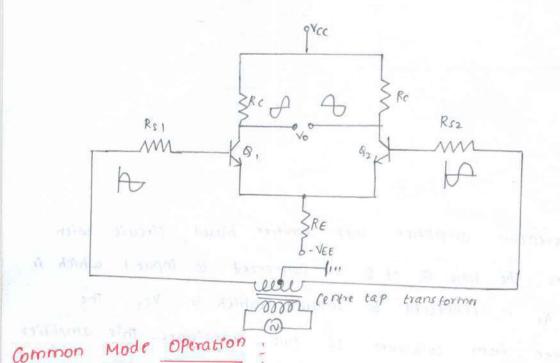

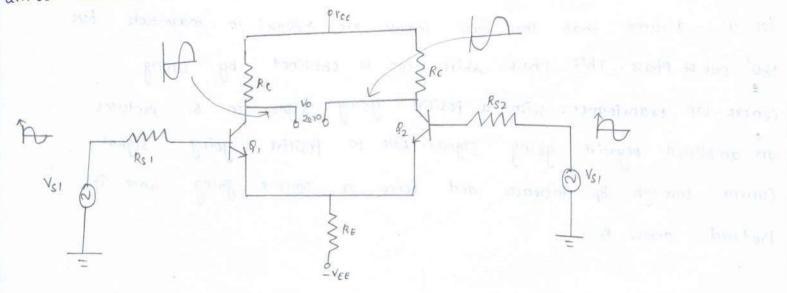

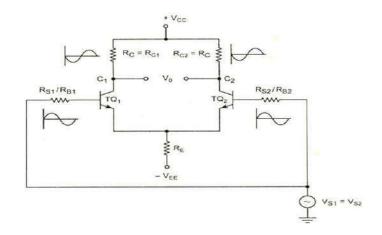

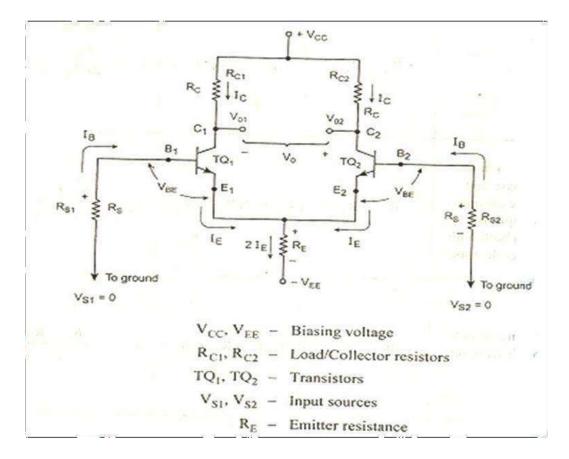

10. Draw the circuit diagram of a symmetrical emitter coupled differential amplifier. [Nov/Dec 2016]

11. Differentiate the ideal and practical characteristics of an op-amp[May/June 2016]

| Characteristics        | Ideal                      | Practical |

|------------------------|----------------------------|-----------|

| Open loop voltage gain | $\infty$                   | High      |

| Input impedance (Ri)   | œ                          | High      |

| Output impedance (Ro)  | 0                          | Low       |

| Bandwidth (BW)         | œ                          | High      |

| Zero offset            | Vo = 0, when $V1 = V2 = 0$ | Non zero  |

12. An operational amplifier has a slew rate of  $4v/\mu s$ . Determine the maximum frequency<br/>of operation to produce distortion less output swing of 12V[April/May 16]Frequency  $f = slewrate(SR) / 2\Pi Vm$

$$= 4 / (2* \Pi * 12)$$

$$= 0.013 \text{ Hz}$$

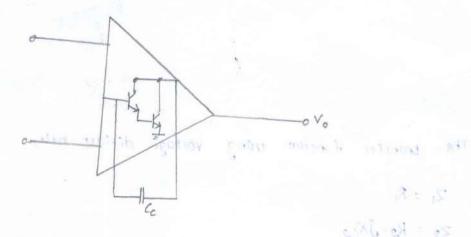

13. What is the cause for slew rate and how it can be made faster? [April/May 2015]

There is a capacitor within or outside an op-amp to prevent oscillation. It is this capacitor which prevents the output voltage from responding immediately to a fast changing input .The slew rate can be made faster by having a higher current or a small compensating capacitor

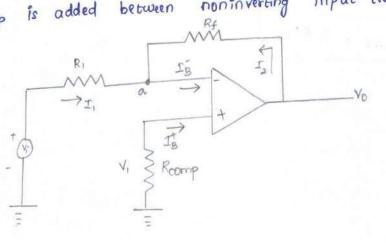

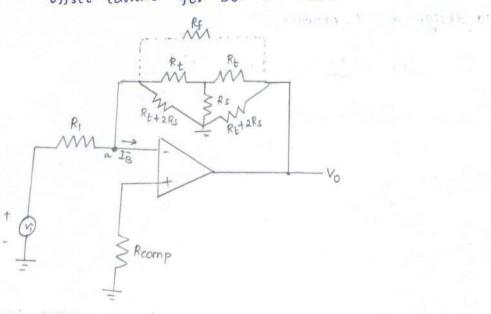

14. Define input bias current and input offset current of an operational amplifier

[Nov/Dec 2015]

Input bias current is the average value of the base current entering in to the i/p terminals of an opamp.Its typical value is 500nA

Input offset current is the algebraic difference between the current into the inverting and non-inverting terminals is referred to as input offset current  $I_{\rm io}$ . Mathematically it is represented as

$I_{io} = |I_{B^+} - I_{B^-}|$

Where IB+ is the current into the non-inverting input terminals.

IB- is the current into the inverting input terminals.

15. Mention two advantages of active load over passive load in an operational amplifier

[Nov/Dec 2015]

[Mav/June 2013]

- Larger gain

- Larger Bandwidth

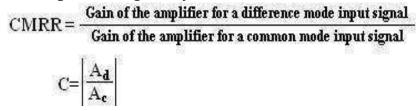

- 16. A differential amplifier has a differential voltage gain of 2000 and a common mode<br/>gain of 0.2.Determine the CMRR in dB[April/May 2015]

Given common mode gain A<sub>cm</sub>=0.2

Difference mode gain A<sub>dm</sub>=2000

$$CMRR = A_{dm} / A_{cm} = 2000 / 0.2 = 10000 = 10 \log 10000 = 80 dB$$

17. Define Slew rate and what causes slew rate?[April/May 2015]

The slew rate of an op amp or any amplifier circuit is the rate of change in the output voltage caused by a step change on the input.

There is usually a capacitor within or outside an op-amp to prevent oscillation. It is this capacitor which prevents the output voltage from responding immediately to a fast changing input

18. Define CMRR of an operational amplifier?

The common mode rejection ratio (CMRR) can be defined as the ratio of differential gain to common mode gain.

$$CMRR = |Ad/Ac|$$

19. Define integrated circuit.

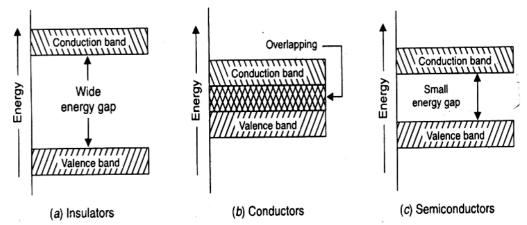

An integrated circuit (IC) is a miniature, low cost electronic circuit consisting of active and passive components fabricated together on a single crystal of silicon. The active components are transistors and diodes and passive components are resistors inductors and capacitors

## 20. What are the advantages of integrated circuits over discrete components?

- i. Miniaturization and hence increased equipment density.

- ii. Cost reduction due to batch processing.

- iii. Increased system reliability due to the elimination of soldered joints.

- iv. Improved functional performance.

- v. Matched devices.

- vi. Increased operating speeds.

- vii. Reduction in power consumption

## 21. What are the disadvantages of integrated circuits?

- Inductors can't be fabricated

- IC's function at fairly low voltage

- They can handle only limited amount of power.

- It can't withstand for rough handling and excessive heat

22. What is meant by monolithic IC

A monolithic integrated circuit (IC) is an electronic circuit that is built on a single semiconductor base material or single chip

23. What is current mirror?

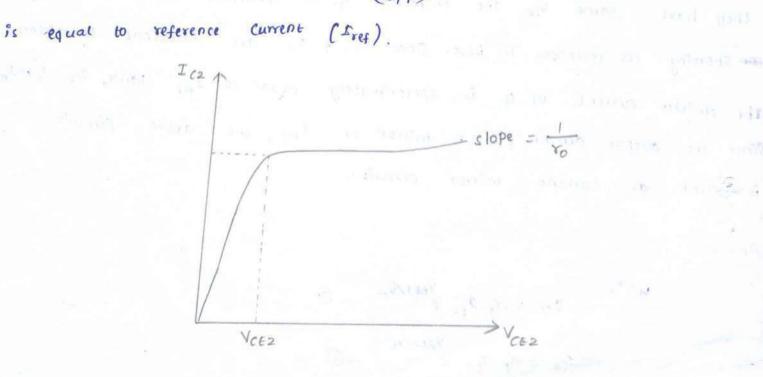

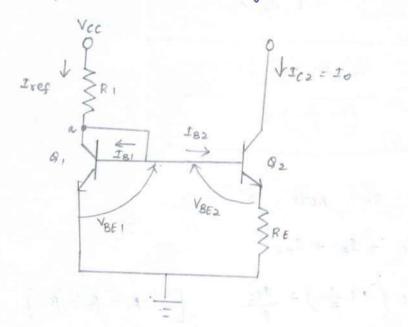

The circuit in which the output current is forced to equal the input current is called as current mirror circuit. The current mirror makes use of the fact that for a transistor in the active mode of operation, the collector current is relatively independent of the collector voltage. In this the output current is a reflection or mirror of the reference current.

24. What are the two requirements to be met for a good current source?

A good current source must meet two requirements:

- 1. Output current  $I_0$  should not depend on  $\beta$ ;

- 2. Output Resistance (RO) of the current source should be very high;

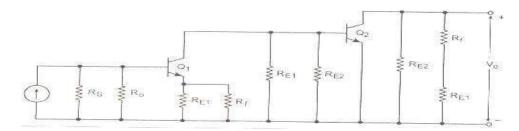

- 25. List the various methods of realizing high input resistance in a differential amplifier. The various methods of realizing high input resistance in a differential amplifier circuits are

(i) Use of Darlington pair

(ii) Use of FET

(iii) Use of swamping resistors.

26. What is active load? Where it is used and why?

In circuit design, an active load is a circuit component made up of active devices, such as transistors, intended to present a high small-signal impedance yet not requiring a large DC voltage drop, as would occur if a large resistor were used instead. Such large AC load impedances may be desirable, for example, to increase the AC gain of some types of amplifier.

Most commonly the active load is the output part of a current mirror and is represented in an idealized manner as a current source. Usually, it is only a constantcurrent resistor that is a part of the whole current source including a constant voltage source as well

27. Explain the limitation of current mirror circuits?

For low value of current source, the value of resistance R should be high which can't be fabricated economically in an Ic circuits.Widlar current source is suitable for low value.

28. Draw the circuit of a Widlar current source and write the exp for its output current. (May 2007)

Ic1 =  $(\beta/\beta+1)$  Iref Iref = VCC -VBE / R1 For  $\beta >>1$ , Ic1 = Iref

29. Draw the basic current mirror circuit.

30. Draw the Wilson current source.

31. Define Thermal Drift.

The change in bias current ,offset voltage and offset voltage for each degree Celsius change in temperature .The offset current drift is expressed in A/ $^{\circ}$ c and offset voltage drift in V/ $^{\circ}$ c

32. What is an operational amplifier?

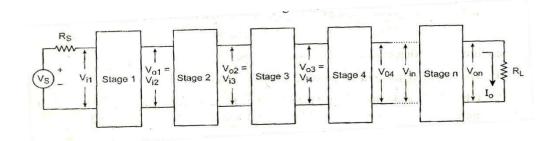

The operational amplifier is a multi-terminal device, which is quite complex internally. An operational amplifier is a direct coupled high gain amplifier usually consisting of one or more differential amplifiers and usually followed by a level translator and an output stage. An operational amplifier is available as a single integrated circuit package. It is a versatile device that can be used to amplify dc as well as ac input signals and was originally designed for computing such mathematical functions.

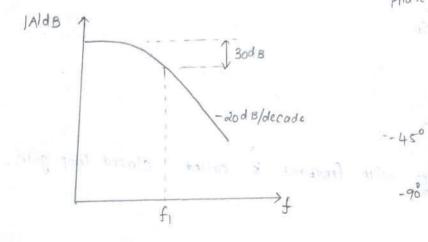

- 33. What are the AC characteristics of an op-amp?

- Frequency response

- Slew rate

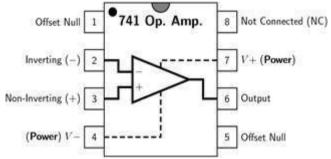

- 34. What are the DC characteristics of an op-amp? Give the typical values for an IC741?

- 1. Input bias current: 500 nA

- 2. Input offset current: 200 nA

- 3. Input offset voltage: 6mV

- 4. Thermal drift

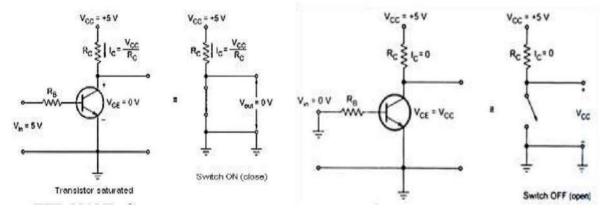

- 35. When does the op-amp behave as a switch?

When op-amp is operating in open loop mode it acts as a switch. Consider two signals V1 and V2 applied at both inverting and non-inverting terminal respectively. Since the gain of the op-amp is infinite, the output V0 is either at its positive saturation voltage (+Vsat) or negative saturation voltage (-Vsat) as V1 > V2 or V2 – V1 respectively. Therefore amplifier acts as a switch.

36. In response to square wave input, the output of an op-amp changed from -3V to +3V over a time interval of 0.25 µs. Determine the slew rate of the op-amp.

Slew rate = dvc/dt / max

$$= \Delta Vo/\Delta t$$

$$= 6V / 0.25 \mu S$$

$$= 1.5 \ V/\mu S$$

37. Define supply voltage rejection ratio (SVRR)

The change in OPAMP's input offset voltage due to variations in supply voltage is called the supply voltage rejection ratio. It is also called Power Supply Rejection Ratio (PSRR) or Power Supply Sensitivity (PSS)

38. Define input offset voltage

The input offset voltage is a parameter defining the differential DC voltage required between the inputs of an amplifier, especially an operational amplifier (op-amp), to make the output zero

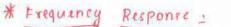

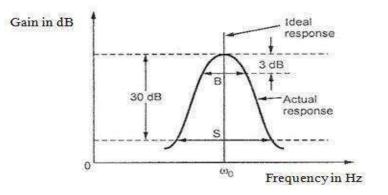

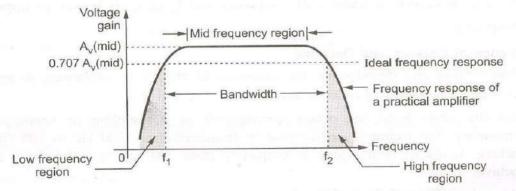

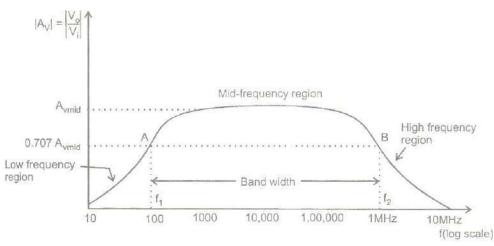

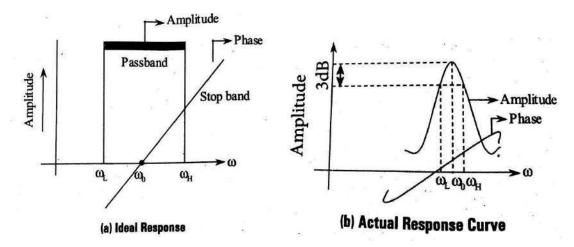

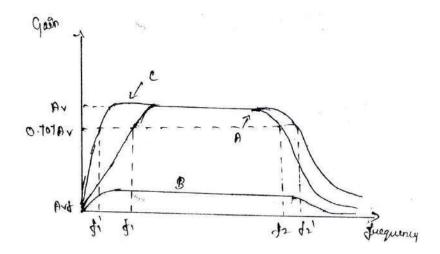

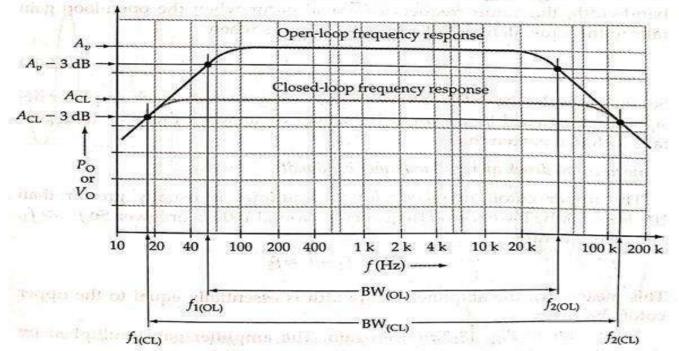

## 39. Define Frequency Response

Frequency response is the quantitative measure of the output spectrum of a system or device in response to a stimulus, and is used to characterize the dynamics of the system. It is a measure of magnitude and phase of the output as a function of frequency, in comparison to the input.

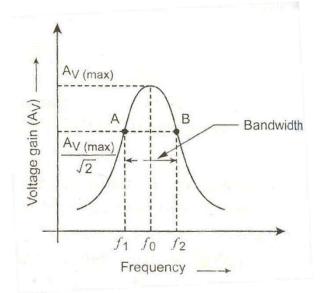

40. Define unity gain bandwidth of a Op-Amp

The GBWP (Gain Band Width Product) of an operational amplifier is 1 MHz, it means that the gain of the device falls to unity at 1 MHz. Hence, when the device is wired for unity gain, it will work up to 1 MHz (GBWP = gain × bandwidth, therefore if BW = 1 MHz, then gain = 1) without excessively distorting the signal.

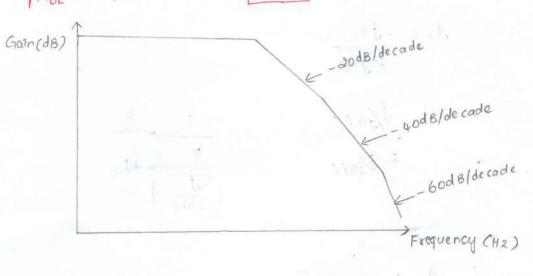

41. Why IC 741 is not used for high frequency applications?

IC741 has a low slew rate because of the predominance of capacitance present in the circuit at higher frequencies. As frequency increases the output gets distorted due to limited slew rate.

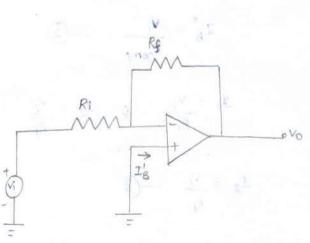

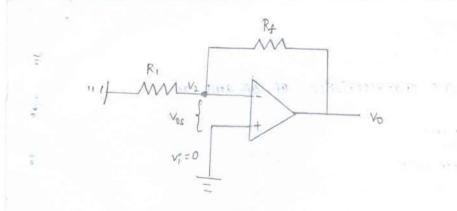

42. Why do we use  $R_{comp}$  resistor?

$R_{\text{comp}}$  is used to compensate for input bias current, which is added between non inverting input terminal of op-amp and ground.

43. What is the gain cross over and phase cross over frequencies?

The gain crossover frequency, wgc, is the frequency where the amplitude ratio is 1, or when log modulus is equal to 0.

The phase crossover frequency, wpc, is the frequency where phase shift is equal to -1800.

44. State loading effect?

Load effect is a power supply specification (also known as load regulation) that describes how well the power supply can maintain its steady-state output setting when the load changes

45. What are the applications of current sources?

The Current sources are used as the emitter resistance in differential amplifier to increase CMRR and as an active load to provide high a.c resistance without disturbing the d.c. conditions.

- 46. State the various blocks of IC op-amp

- Input stage

- Intermediate stage

- Level shifting stage

- Output stage

- 47. Why frequency compensation is required?

The op-amp with single break frequency is inherently stable. Practically opamp has more than one break frequencies. It is necessary to provide compensation so that only one break over frequency exist duo to which phase shift of op-amp cannot increase beyond  $-90^{\circ}$ . Hence there is no chance that op-amp phase shift becomes - $135^{\circ}$  and phase margin always remains more than  $+45^{\circ}$ . Hence op-amp becomes inherently stable.

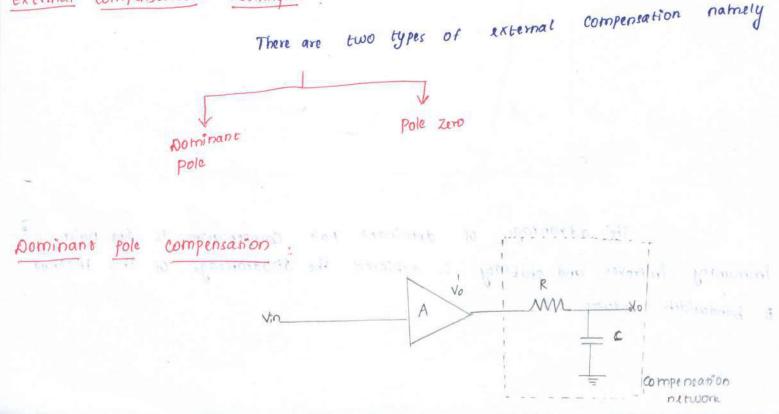

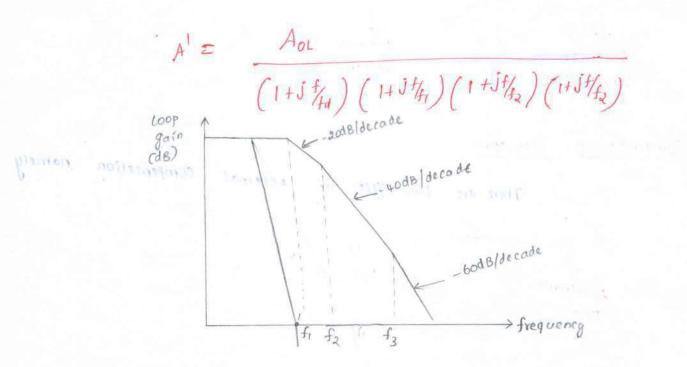

- 48. List the methods used to provide external frequency compensation.

- Dominant pole compensation

- pole zero compensation

- Feed forward compensation

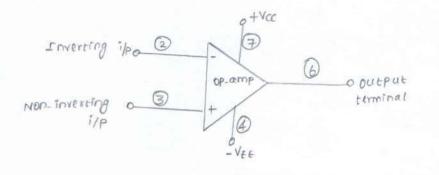

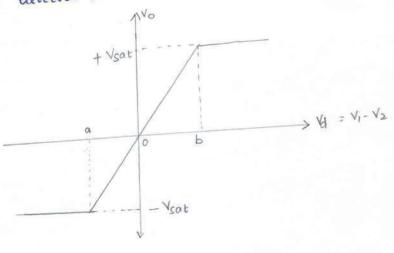

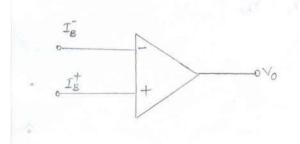

- 49. Draw the op-amp symbol and state its important terminals.

Important terminals are

- Inverting input

- Non inverting input

- Positive supply

- Negative supply

- output

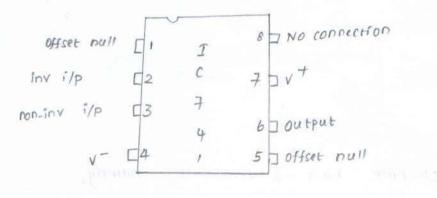

- 50. Draw the pin diagram of IC741

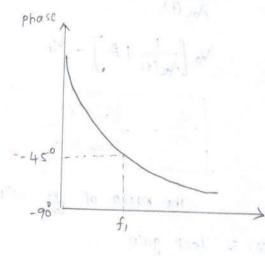

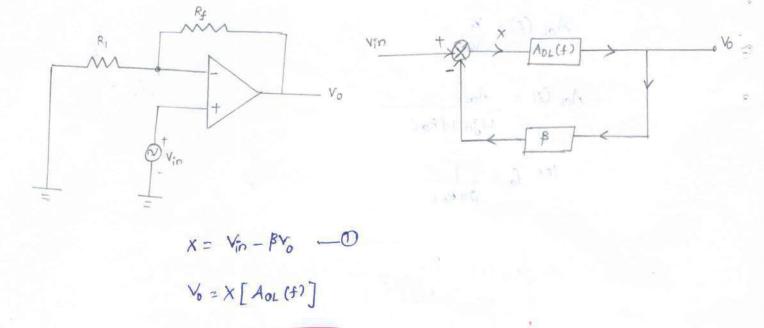

51. Why op-amp in open loop is not used for most of the applications?

The open loop gain of op-amp is very large and hence the output saturates at supply voltage which are of the order of few volts. Thus linear operation of op-amp is possible only for very small range of input voltage of the order of few millivolts. This is not sufficient for most of the practical applications. Hence op-amp in open loop is not used for most of the applications

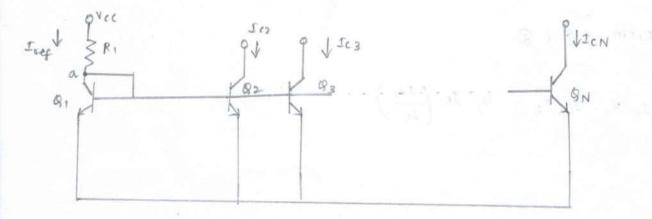

52. Define current mirror with magnification.

A current mirror circuit in which the ratio of the biasing currents in two transistors are fixed, is called current mirror with magnification.

## PART – B&C

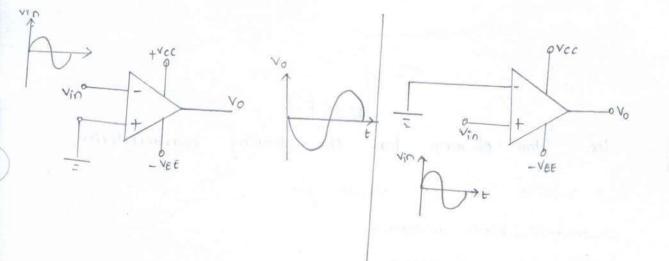

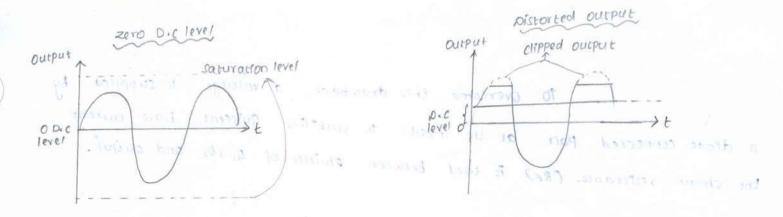

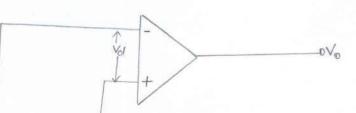

- (i) Draw the transfer characteristics of an operational amplifier and explain its linear and non linear operations.

(8) [Nov/Dec 2017] [Nov/Dec 2018] [Ref .Roy Choudhry, ShailB.Jain, "Linear Integrated Circuits (Fourth Edition)", Page 55]

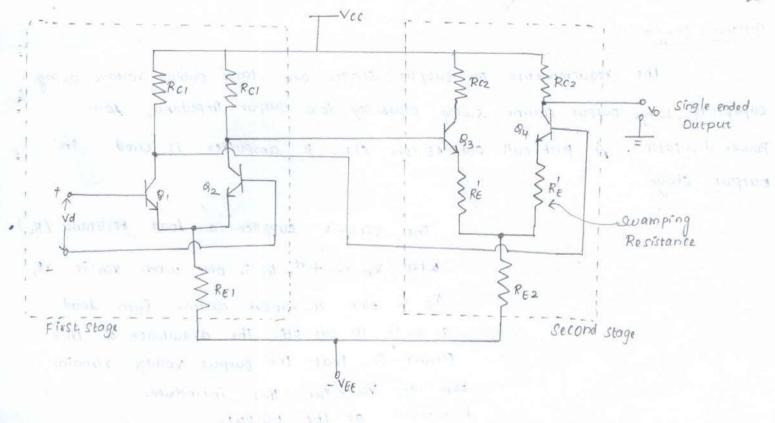

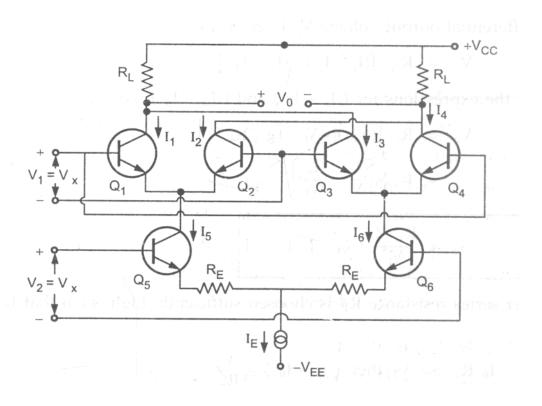

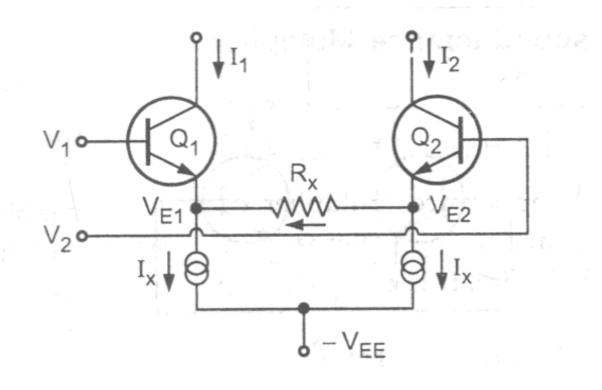

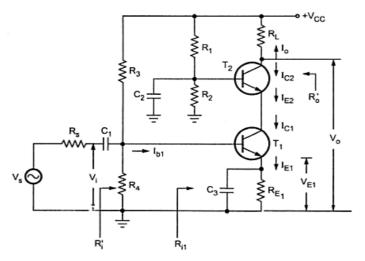

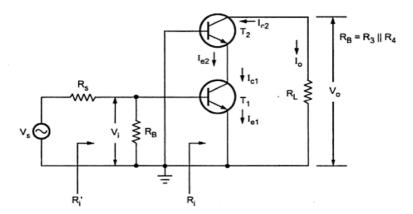

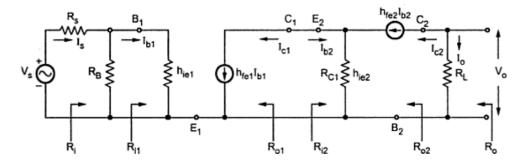

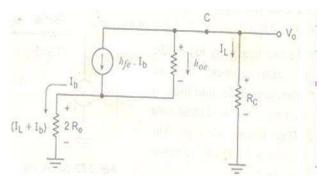

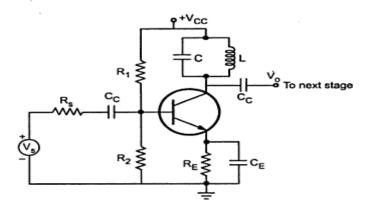

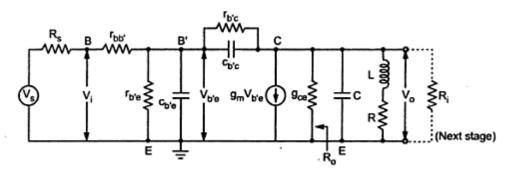

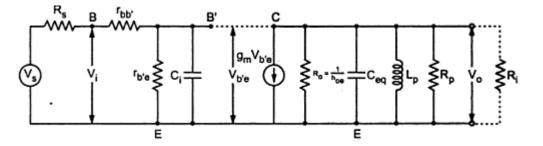

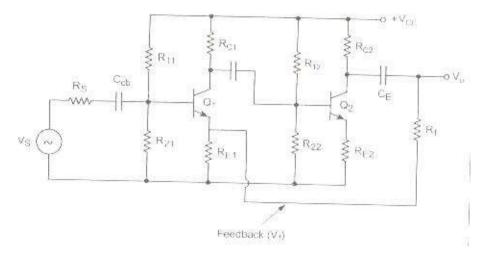

- (ii) Discuss the operation of BJT differential amplifier with active loads.(5) [Nov/Dec 2018]

[Ref .Roy Choudhry, ShailB.Jain, "Linear Integrated Circuits (Fourth Edition)", Page 77]

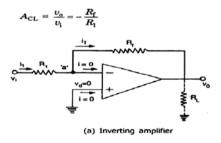

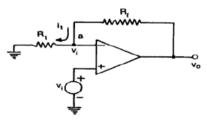

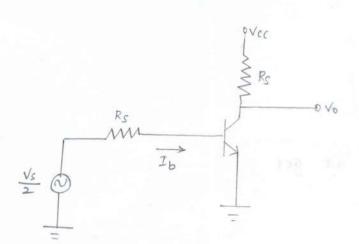

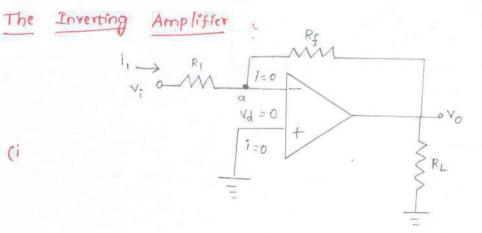

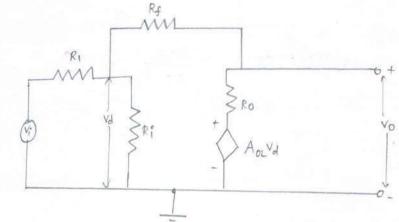

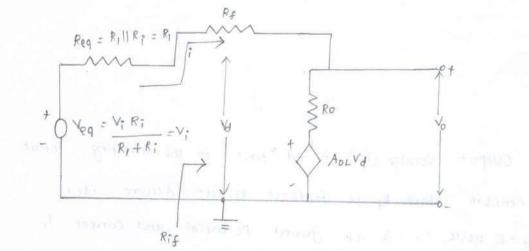

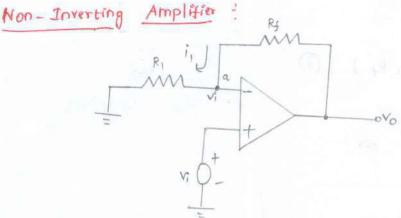

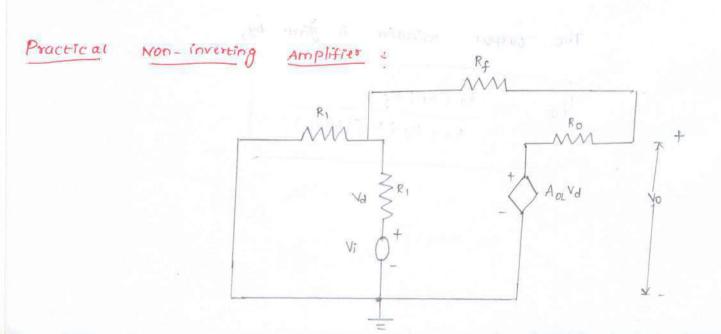

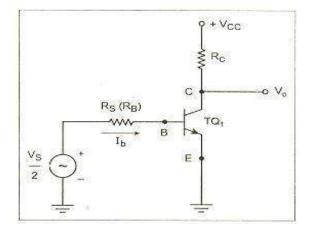

2. (i) Present the inverting and non inverting amplifier circuits of an op-amp in closed loop configuration. Derive the expressions for the closed loop gain in these circuits. (9) [Nov/Dec 2018]

[Ref .Roy Choudhry, ShailB.Jain, "Linear Integrated Circuits (Fourth Edition)", Page 43]

| (ii) | Define slew rate. In what way does it possess impa             | act on the                  |

|------|----------------------------------------------------------------|-----------------------------|

|      | performance of an op-amp circuit (4)                           | [Nov/Dec 2018]              |

|      | [Ref .Roy Choudhry, ShailB.Jain, "Linear Integrated Circuits ( | Fourth Edition)", Page 123] |

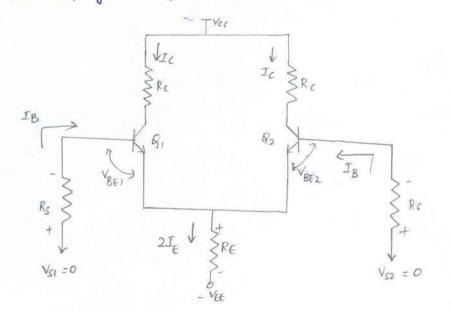

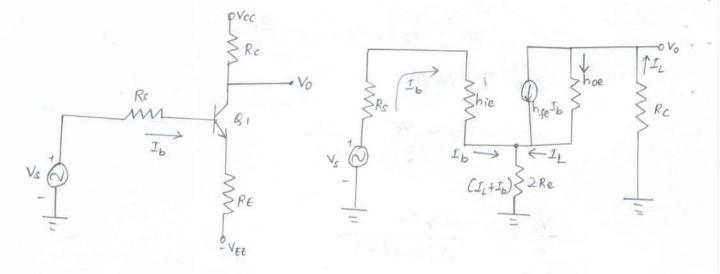

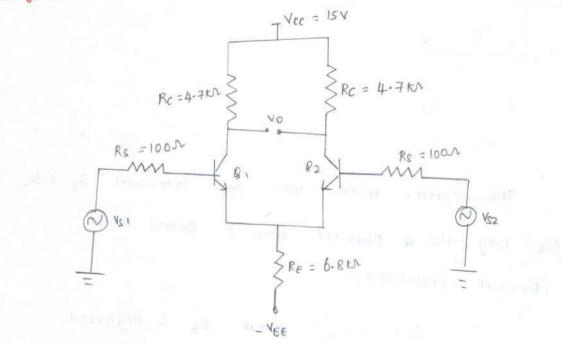

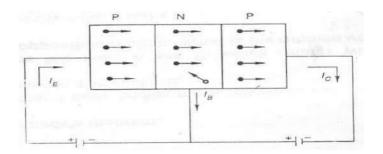

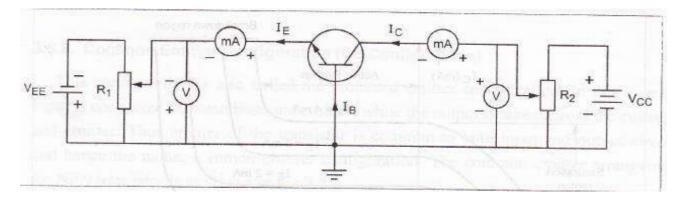

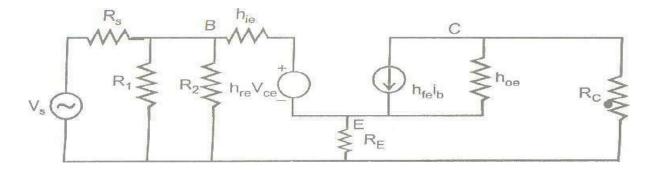

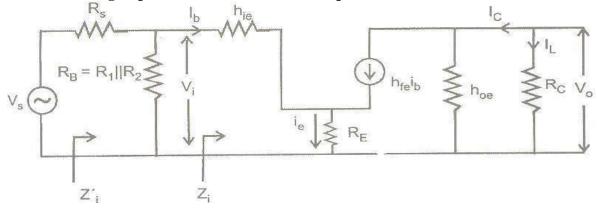

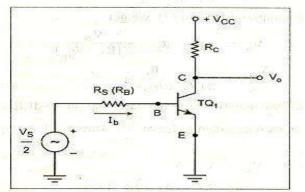

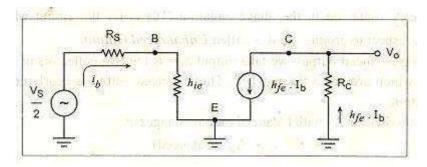

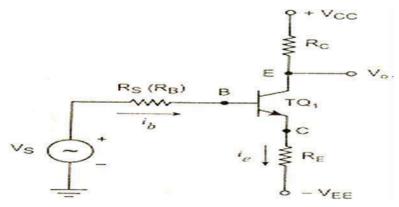

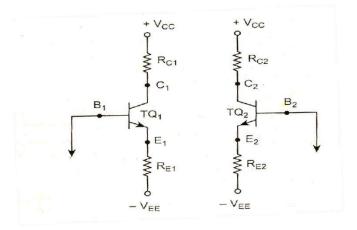

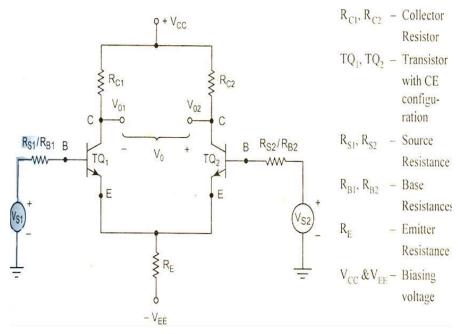

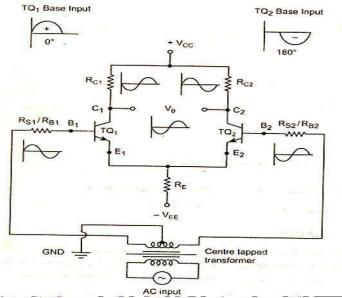

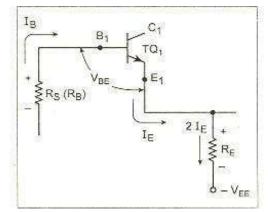

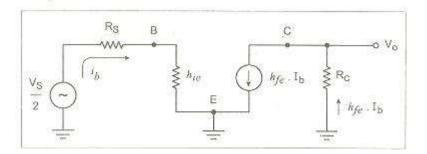

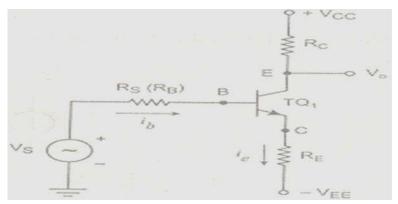

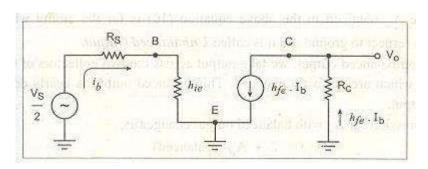

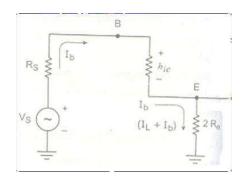

3. Discuss about the principle of operation of differential amplifier using BJT.

## [April/May 2018]

- [Ref .Roy Choudhry, ShailB.Jain, "Linear Integrated Circuits (Fourth Edition)", Page 53]

- 4. Explain about Ideal Op-Amp in detail with suitable diagrams. [April/May 2018] [Ref .Roy Choudhry, ShailB.Jain, "Linear Integrated Circuits (Fourth Edition)", Page 41]

- 5. With a neat diagram Explain the input side of the internal circuit diagram of IC741 [Nov/Dec2015] [Nov/Dec 2017]

[Ref .Roy Choudhry, Shail B.Jain, "Linear Integrated Circuits (Second Edition)", Page 96]

- 6. (i) What is the input and output voltage and current offsets? How are they compensated? [April/May 2017]

[Ref .Roy Choudhry, ShailB.Jain, "Linear Integrated Circuits (Fourth Edition)", Page 108]

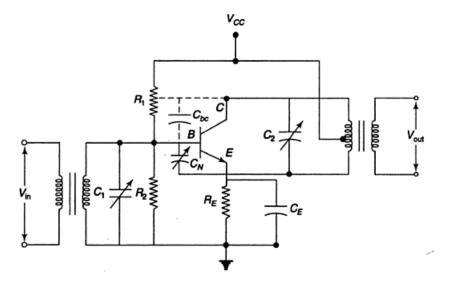

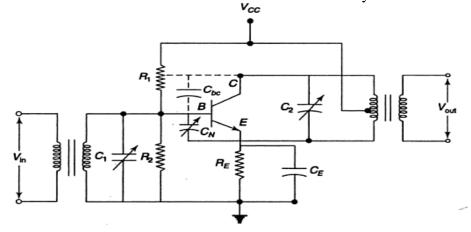

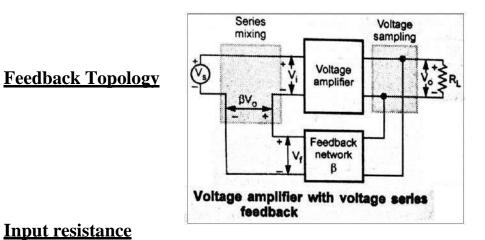

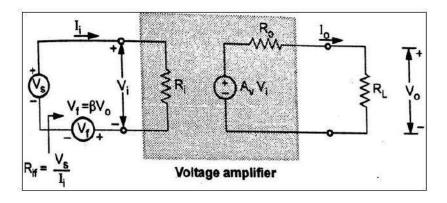

- (ii) With neat diagram derive the AC performance close loop characteristics of Op-Amp to discuss on the circuit Bandwidth, Frequency response and slew rate [April/May 2017]

[Ref .Roy Choudhry, ShailB.Jain, "Linear Integrated Circuits (Fourth Edition)", Page 111]

- 7. i) With a schematic diagram, explain the effect of R<sub>E</sub> on CMRR in differential amplifier [April/May 2016]

[Ref .Roy Choudhry, Shail B.Jain, "Linear Integrated Circuits (Second Edition)", Page 63].

- ii) Discuss about the methods to improve CMRR [April/May 2016]

- 8. (i) With simple schematic of differential amplifier explain the function of Operational Amplifier (8) [April/May 2015]

[Ref .Roy Choudhry, Shail B.Jain, "Linear Integrated Circuits (Second Edition)", Page 63]

- (ii) Briefly Explain about constant current source(8) [April/May2015] [Ref .Roy Choudhry, Shail B.Jain, "Linear Integrated Circuits (Second Edition)", Page 73]

- 9. (i) Briefly explain the techniques used for frequency compensation (12)

#### [April/May2015]

[Ref .Roy Choudhry, Shail B.Jain, "Linear Integrated Circuits (Second Edition)", Page 135]

(ii) How do the open loop gain and the closed loop gain of an op-amp differ? (4)

#### [April/May2015]

[Ref .Roy Choudhry, Shail B.Jain, "Linear Integrated Circuits (Second Edition)", Page 225]

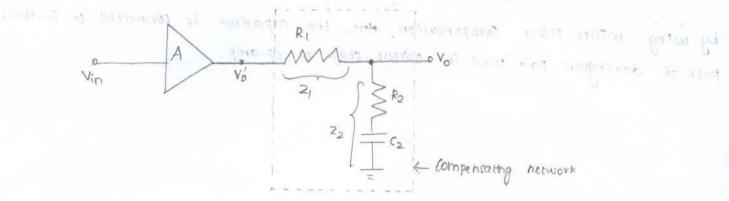

10. What is the need for frequency compensation in an OPAMP? With a suitable illustration, explain the pole-zero frequency compensation technique.

## [Nov/dec 15][April/May 2017]

[Ref .Roy Choudhry, Shail B.Jain, "Linear Integrated Circuits (Second Edition)", Page 135]

- Explain different voltage reference circuit in detail

[Ref .S.Salivahanan & V S Kanchana Baskaran, "Linear Integrated Circuits (Second Edition)", Page 60]

- 12. Explain different voltage sources in detail

[Ref .S.Salivahanan & V S Kanchana Baskaran, "Linear Integrated Circuits (Second Edition)", Page 57]

13. Draw the circuit of basic current mirror and explain its operation. Also discuss about how current ratio can be improved in the basic current mirror.Sketch the improved circuit and explain

[Ref .Roy Choudhry, Shail B.Jain, "Linear Integrated Circuits (Second Edition)", Page 73]

14. (i) Define and explain slew rate. What is full power bandwidth? Also explain the method adopted to improve slew rate

[Ref .Roy Choudhry, Shail B.Jain, "Linear Integrated Circuits (Second Edition)", Page 140]

(ii) Define output off set voltage. Explain methods to nullify offset voltage

- [Ref .Roy Choudhry, Shail B.Jain, "Linear Integrated Circuits (Second Edition)", Page 123] [Ref .Roy Choudhry, Shail B.Jain, "Linear Integrated Circuits (Second Edition)", Page 71]

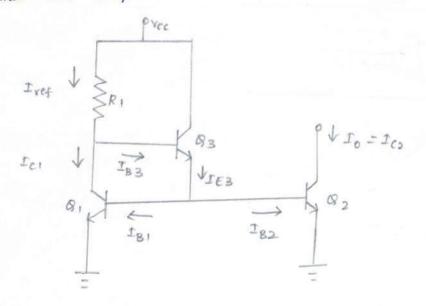

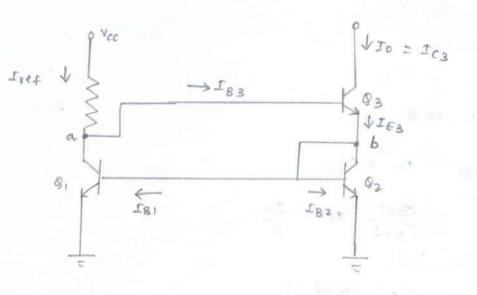

- 15. Explain in detail wilson current source and widlar current source and derive necessary equations

[Ref .Roy Choudhry, Shail B.Jain, "Linear Integrated Circuits (Second Edition)", Page 75]

## UNIT II- APPLICATIONS OF OPERATIONAL AMPLIFIERS Part-A

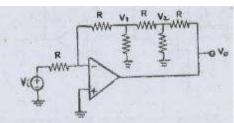

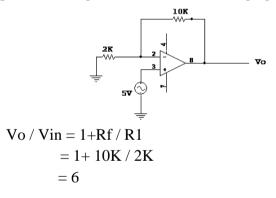

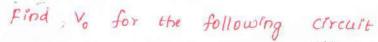

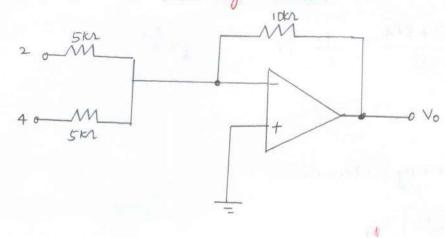

1. Find the gain  $V_o/V_i$  of the circuit

[April/May 2019]

Applying KCL at inverting terminal

$$\frac{0-V_1}{R} = \frac{V_i - 0}{R}$$

V<sub>1</sub>=-V<sub>i</sub>

Applying KCL at node 1

$$\frac{0-V_1}{R} = \frac{V_1}{R} + \frac{V_1 - V_2}{R}$$

V<sub>2</sub> = -3v

Applying KCL at node 2

$$\frac{V_1 - V_2}{R} = \frac{V_2}{R} + \frac{V_2 - V_0}{R}$$

$$8V_i = -V_0$$

$$\frac{V_0}{V_i} = -8$$

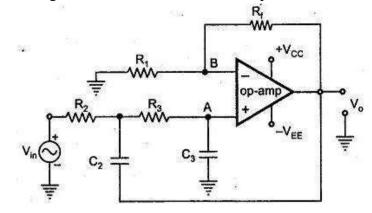

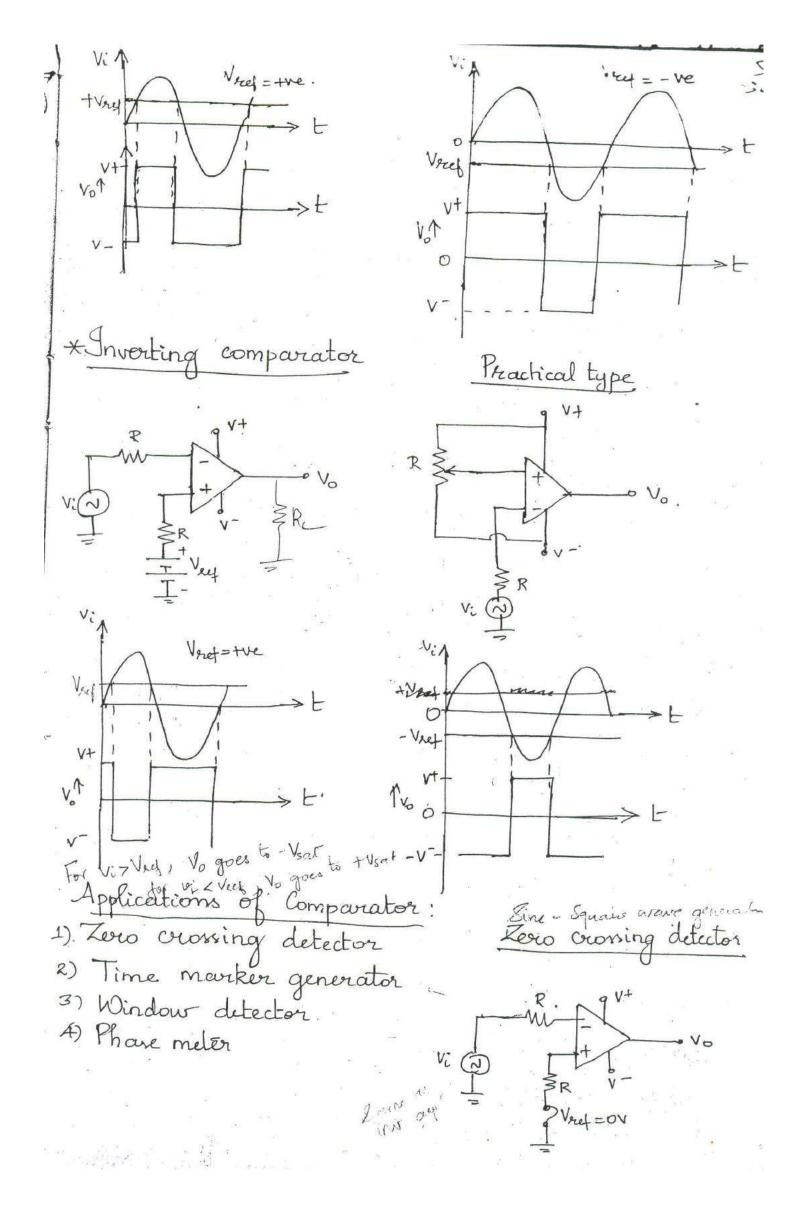

2. How does a zero crossing detector work

Zero crossing detector is one type of voltage comparator used to detect a sine waveform transition from positive and negative that coincides when the input crosses the zero voltage condition

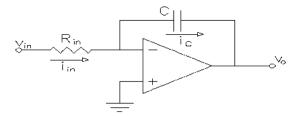

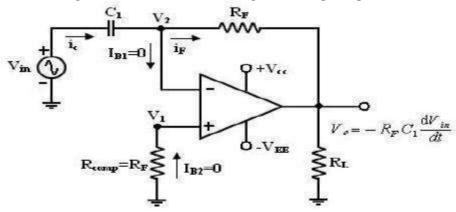

3. How does operational amplifier work as an integrator [Nov/Dec 2018]

By replacing this feedback resistance with a capacitor we now have an RC Network connected across the operational amplifiers feedback path producing another type of operational amplifier circuit called an Op-amp Integrator

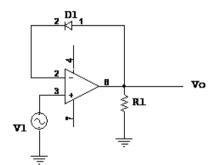

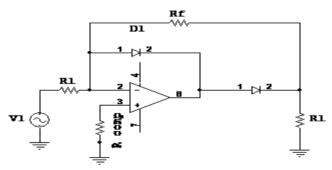

4. Draw the circuit of clipper using op-amp

[Nov/Dec 2018]

[April/May 2019]

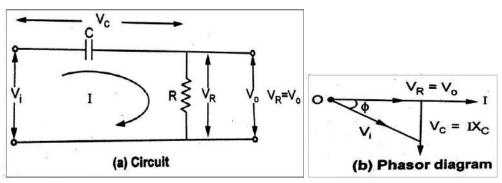

5. What is the function of a phase shift circuit? [April/May 2018]

A phase shifter circuit is one that shifts the relative phase of an input AC signal

- 6. Write the other name for clipper circuit. Other name of clipper circuit is limiter circuit

- 7. State the limitations of an ideal integrator.

- Bandwidth is very small and used for only small range of input frequencies.

[Nov/Dec 2017]

[April/May 2018]

- For dc input (f = 0), reactance of capacitance, Xc is infinite. Because of this opamp goes into open loop configuration. In open loop configuration the gain is infinite and hence the small input offset voltages are also amplified and appears at output as error

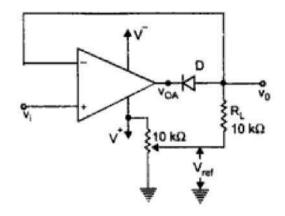

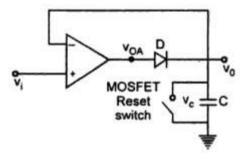

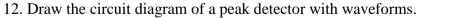

- 8. How will you realize a peak detector using a precision rectifier? [Nov/Dec 2017]

9. What is the need for converting a first order filter into a second order filter?

## [April/May 2017]

A first order active filter has one pole which is defined by a capacitor/resistor pair. A second order filter has two capacitors and resistors. This gives the filters frequency response a steeper slope as it transitions from pass band to stop band

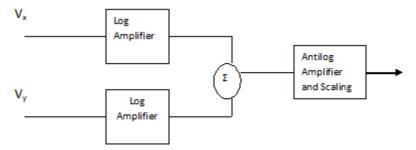

10. How is the current characteristic of a PN junction employed in a Log amplifier?

## [April/May 2017]

The voltage across the diode will be always proportional to the log of the current through it and when a diode is placed in the feedback path of an op-amp in inverting mode, the output voltage will be proportional to the negative log of the input current. Since the input current is proportional to the input voltage, we can say that the output voltage will be proportional to the negative log of the input voltage

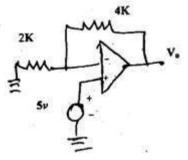

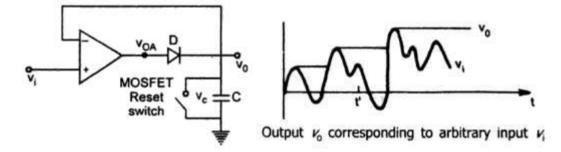

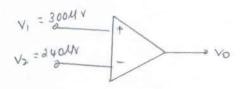

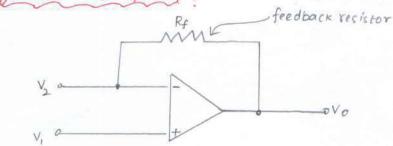

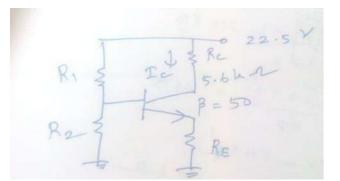

11. For the op-amp shown in figure determine the voltage gain [Nov/Dec 2016]

The given circuit is inverting amplifier

For inverting amplifier voltage gain =  $-\frac{R_f}{R_f}$

$$= -\frac{4k}{2k} = -2$$

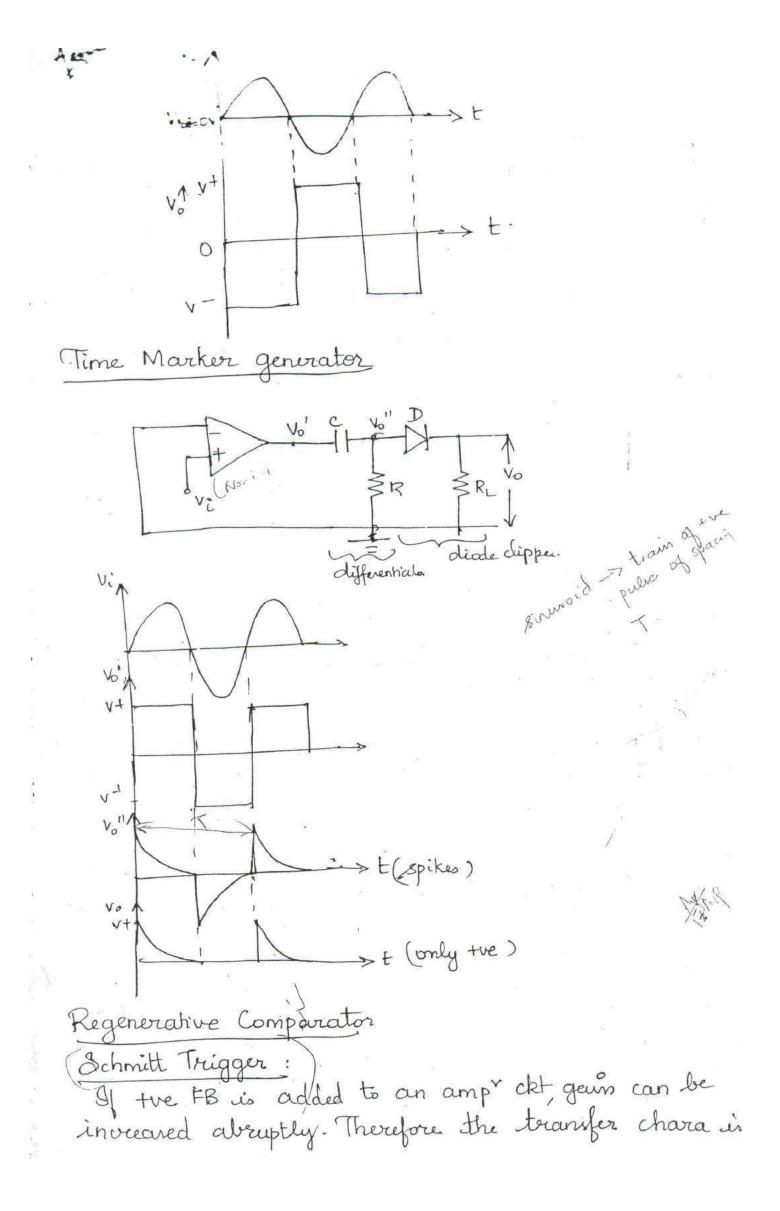

- 13. Give any four applications of comparators. [May/June 2016]

- Zero crossing detector

- Window detector

- Time marker generator

- Phase meter

14. What is hysteresis and mention the purpose of hysteresis in a comparator?

## [April/May 2015]

Hysteresis is the time-based dependence of a system's output on present and past inputs. The dependence arises because the history affects the value of an internal state. To predict its future outputs, either its internal state or its history must be known.

In comparator hysteresis has the effect of separating the up-going and downgoing switching points so that, once a transition has started, the input must undergo a significant reversal before the reverse transition can occur.

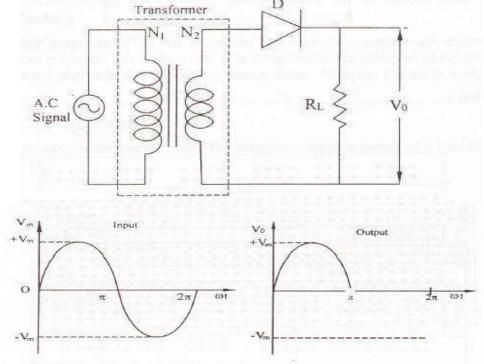

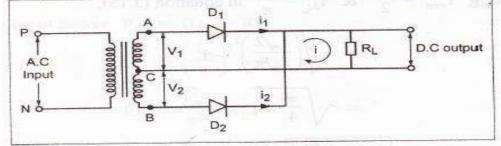

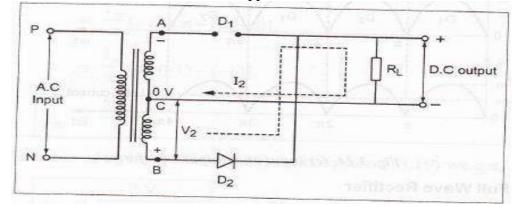

15. What is the difference between normal rectifier and precision rectifier?

## [April/May 2015]

A simple rectifier circuit uses a diode. The input voltage has to exceed the turn-on voltage (0.6V for ordinary Si diode) before rectification is achieved. A precision rectifier is an active circuit using an opamp and a diode in the feedback loop. This overcomes the turn-on "knee" voltage

16. Plot the transfer characteristics of the circuit shown in figure 2 .The op-amp saturates at +/-12V [Nov/Dec 2015]

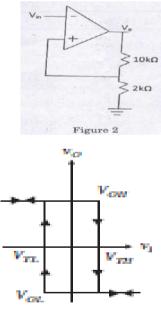

17. Determine the output voltage for the circuit shown in figure 1 when

- (a) Vin=-2V

- (b) Vin=3V [Nov/Dec 2015]

This is basic comparator circuit when Vin=-2V then Vo=10V When Vin =3V then Vo=-10V

18. Define inverting amplifier and draw the circuit?

The input  $v_{in}$  is given to the second pin of op-amp through the input resistance  $R_1$  the feedback resistor  $R_f$  connects the output and input pin and the output is always reversed or inverted.

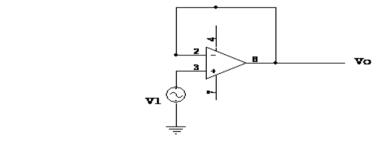

19. Define non-inverting amplifier and draw the circuit?

The input  $v_{in}$  is given to the non-inverting terminal pin 3 of op-amp. The input resistor R1 & the feedback resistor R<sub>f</sub> are connected to the inverting input only ,the input pin and the output is always same phase.

(a) Non-inverting amplifier

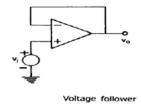

20. What is meant by voltage follower?

In the non-inverting amplifier, if  $R_f=0$  and  $R_1=\infty$  then the modified circuit is called voltage follower or unity gain amplifier.

21. Draw the circuit diagram of an op-amp integrator. Mention its applications.

Application:

- 1. It is generally used in analog computer and analog to digital converter.

- 2. It also used in wave shaping circuits

- 22. Draw the circuit diagram of an op-amp differential amplifier. Mention its o/p equation.

$$v_{\rm o} = \frac{R_2}{R_1} \, (v_1 - v_2)$$

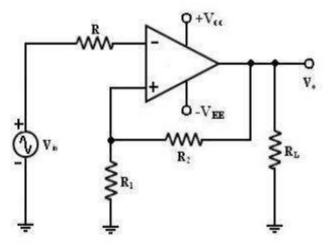

23. For the op-amp shown in figure, determine the voltage gain.

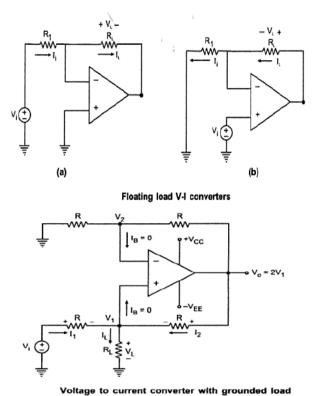

24. Explain the voltage to current convertor

Voltage to current convertor converts an input signal voltage to a proportional output current. According to the connection of load there are two types of voltage to current convertor

- 1. Floating type

- 2. Grounded type

25. Draw the circuit of a voltage follower using op-amp and prove that its gain is exactly equal to unity.

- Vo / Vin = 1 + Rf / R1; Vo / Vin = 1 + 0; Vo / Vin = 1.

- 26. An ac signal has got a magnitude of 0.1 volt peak to peak. Suggest a suitable half wave rectifier for this signal.

27. Derive the expression for voltage gain of an inverting operational amplifier?

ACL = Vo/Vi = -Rf / R1

28. Mention two linear and two non- linear operations performed by an operational amplifier?

Linear operations: Adder, Subtractor, Voltage to current converter, Current to voltage converter, Instrumentation amplifier, Analog computation, and Power amplifier.

Non-linear operations: Rectifier, Peak detector, Clipper, Clamper, Sample and hold circuits, Log and antilog amplifier and Multiplier.

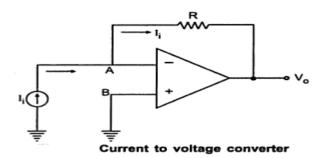

29. Draw the circuit of current to voltage convertor?

- 30. Mention two application of Schmitt trigger?

- For eliminating comparator chatter.

- In ON/ OFF controller.

- Square wave generation

- 31. Mention the characteristics of Instrumentation amplifier?

- High gain

- High CMRR

- High gain stability

- Low dc offset

- Low output impedance

- Low power loss

- High input impedance

32. State the disadvantages of passive filters?

At audio frequencies inductors becomes problematic, as the inductors become large,

heavy and expensive. For low frequency application, more number of turns of wire must be used which in turn adds to the series resistance degrading inductors

performance.

33. What is Precision rectifier?

It is a rectifier circuit which utilities precision diode instead of usual diodes for rectification purpose in order to operate them for cut-in voltages in the order of microvolt.

34. Define precision half wave rectifier with diagram?

It is defined as a circuit, which utilizes two precision diodes instead of usual diodes for rectification purpose in order to operate them for, cut in voltages in the order of micro volts.

35. What are the main drawbacks of ideal differentiator?

At high frequency, differentiators may become unstable and break into oscillation. The input impedance i.e.  $(1/\omega C1)$  decreases with increase in frequency, thereby making the circuit sensitive to high frequency noise.

36. What are the steps to be followed while designing a good differentiator?

Choose  $f_b=10f_a$  (Say). Now calculate the values of R1 and C1.

R1C1 = RfCf.

37. What are the main drawbacks of ideal integrator circuit?

At low frequencies such as dc ( $\omega \approx 0$ ) the gain becomes infinite.

When the op-amp saturates i.e. the capacitor is fully charged it behaves like an open circuit.

38. Give the output voltage when  $V_i$  is positive and negative in a precision diode.

When Vi is positive, diode D1 conducts causing V0 to negative by one diode drop (Vr =0.6v). Hence, diode D2 is reverse biased. The output voltage V0 is zero.

When Vi is negative ie Vi < 0, diode D2 conducts D1 is off. The negative input Vi forces the op-amp circuit VON positive and causes D2 to conduct. Output  $V_0$  becomes positive.

39. Give an application of an Inverting Amplifier.

1.Sign Changer

2. Scale changer

40. Draw the circuit diagram of a schmitt trigger

41. What is a filter?

Filter is a frequency selective circuit that passes signal of specified band of frequencies and attenuates the signals of frequencies outside the band

42. Draw the circuit diagram of differentiators and give its output equation

- 43. State the applications of V-I converter

- Low voltage d.c voltmeter

- Low voltage a.c voltmeter

- Diode tester

- Zener diode tester

- 44. State the applications of current to voltage converter

- Photodiode detector

- PhotoFET detector

- 45. List the applications of differentiator circuit.

- In the wave shaping circuits

- To detect high frequency components in the input.

- As a rate of change detector in the FM demodulator

- 46. List various applications of comparator.

- Zero crossing detector

- Window detector

- Level detector

- 47. What is a zero crossing detector?

A circuit which detects the crossing of zero level by the input signal is called a zero crossing detector. An op-amp comparator is used as a zero crossing detector.

48. When inverting amplifier is called phase inverter?

When the gain of inverting amplifier is unity and is used to change the phase of the input to produce the output then it is called phase inverter.

- 49. State any four applications of instrumentation amplifier,

- Temperature controller

- Data acquisition system

- Light intensity meter

- Analog weight scale

- 50. Why temperature compensation is required for log amplifiers?

The reverse saturation current  $I_o$  for the diode changes with temperature and it doubles for every ten degree celicius rise in the temperature. Similarly the emitter saturation current varies significantly from one transistor to other and also with temperature. Hence it is very difficult to set the term  $V_{ref}$  for the circuit. The term  $V_T$ which is KT also changes with temperature, which appears in the final equations. Hence temperature affects the performance and accuracy of the basic logarithmic amplifier circuit. Hence it is must to provide some sort of temperature compensation to reduce the errors.

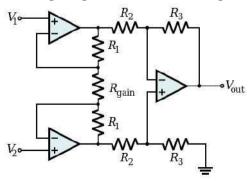

51. Draw the circuit diagram of 3 op-amp instrumentation amplifier.

52. Draw the circuit diagram of second order active low pass Butterworth filter

## PART-B&C

| 1. | (i)        | With suitable circuit diagram ,explain the operating princip                 | ole of an              |

|----|------------|------------------------------------------------------------------------------|------------------------|

|    |            | instrumentation amplifier and derive its gain.(7)                            | [Nov/Dec 2018]         |

|    |            | [Ref .Roy Choudhry, ShailB.Jain, "Linear Integrated Circuits (Fourth 1       | Edition)", Page 141]   |

|    | (ii)       | Design a second order butterworth low-pass filter having u                   | pper cut-off           |

|    |            | frequency of 2.1961 kHz (6)                                                  | [Nov/Dec 2018]         |

|    |            | [Ref .Roy Choudhry, ShailB.Jain, "Linear Integrated Circuits (Fourth 1       | Edition)", Page 269]   |

| 2. | (i)        | Design a clipper circuit for a clipping level of +0.83V, give                | en an input            |

|    |            | sine wave signal of 0.3V peak. Assume the gain of the am                     | plifier is 9           |

|    |            | and it has an input resistance of 2.2k-ohm connected.(5)                     | [Nov/Dec 2018]         |

|    |            | [Ref .Roy Choudhry, ShailB.Jain, "Linear Integrated Circuits (Fourt          | h Edition)", Page 151] |

|    | (ii)       | Draw the operational diagram and explain the working prin                    | nciple of              |

|    |            | antilogarithmic amplifier and Schmitt trigger.(8)                            | [Nov/Dec 2018]         |

|    |            | [Ref .Roy Choudhry, ShailB.Jain, "Linear Integrated Circuits (Fourt          | h Edition)", Page 157] |

| 3. | i)         | Describe about voltage follower circuit.(7)                                  | [April/May 2018]       |

|    |            | [Ref .Roy Choudhry, ShailB.Jain, "Linear Integrated Circuits (Fourth ]       |                        |

|    |            | ii) Write short notes on subtractor circuit(6)                               | [April/May 2018]       |

|    |            | [Ref .Roy Choudhry, ShailB.Jain, "Linear Integrated Circuits (Fourth         |                        |

| 4. | With a     | a neat diagram Explain about V-I conveter.                                   | [April/May 2018]       |

| _  |            | [Ref .Roy Choudhry, ShailB.Jain, "Linear Integrated Circuits (Fourth ]       |                        |

| 5. | (i)        | For performing differentiation in an operational amp                         | e e                    |

|    |            | preferred to differentiator-Explain                                          | [Nov/Dec 2017]         |

|    | <i>(</i> ) | [Ref .Roy Choudhry, ShailB.Jain, "Linear Integrated Circuits (Fourth         |                        |

|    | (ii)       | What is instrumentation amplifier? Draw a system whose g                     | •                      |

|    |            | a variable resistance                                                        | [Nov/Dec 2017]         |

|    |            | [Ref .Roy Choudhry, ShailB.Jain, "Linear Integrated Circuits (Fourth 2 &142] | Edition)", Page 141    |

| 6. | Fynlai     | in the operation of differentiator and integrator with relev                 | vant waveforms and     |

| 0. | equati     |                                                                              | [April/May 2017]       |

| 7. | -          | Design a differentiator to produce an output of 6 V when the                 |                        |

|    |            | changes by 2V in 40 micro seconds. (5)                                       | [Nov/Dec 2018]         |

|    |            | [Ref .Roy Choudhry, Shail B.Jain, "Linear Integrated Circuits (Second        | l Edition)", Page 170] |

|    | (ii)       | Write short notes on Clipper and clamper circuits(8)                         | [April /May 2017]      |

|    | -          | Roy Choudhry, ShailB.Jain, "Linear Integrated Circuits (Fourth Edition       |                        |

| 8. | With a     | a neat block diagram explain the stages for developing the si                | gnal analysis          |

|    | circuit    | s required for an instrumentation module of say a vibration                  | sensor data using      |

instrumentation amplifier, waveshaper, and comparator for ADC using OPAMP and required components

[Ref .Roy Choudhry, ShailB.Jain, "Linear Integrated Circuits (Fourth Edition)", Page 141]

[Ref .Roy Choudhry, Shail B.Jain, "Linear Integrated Circuits (Second Edition)", Page 186]

- 9. i) Draw the circuit of a second order Butterworth active low pass filter and derive its transfer function. [April/May 2016] [Ref .Roy Choudhry, Shail B.Jain, "Linear Integrated Circuits (Second Edition)", Page 293]

- ii) Design a second order active low pass filter for a cut-off frequency of 1 KHz. [April/May 2016]

[Ref .Roy Choudhry, Shail B.Jain, "Linear Integrated Circuits (Second Edition)", Page 293] 10. Explain the working of 3 op-amp Instrumentation amplifier?

## [April/May 2018][ [April/May2016]

[Ref .Roy Choudhry, Shail B.Jain, "Linear Integrated Circuits (Second Edition)", Page 161]

- Briefly explain the working principle of Schmitt trigger. 11. i) [Ref .Roy Choudhry, Shail B.Jain, "Linear Integrated Circuits (Second Edition)", Page 237]

- Design a wide band pass filter having  $f_L=400$  Hz  $f_H=2kHz$  and pass band ii) [April/May 2015] gain of 4. Find the value of O of the filter [Ref .Roy Choudhry, Shail B.Jain, "Linear Integrated Circuits (Second Edition)", Page 306]

- 12. With a circuit diagram discuss the following applications of op-amp.

- a. Voltage to current converter.

b.Precision rectifier.

[Ref .Roy Choudhry, Shail B.Jain, "Linear Integrated Circuits (Second Edition)", Page 166 &169] 13. Explain the working of Log amplifier and antilog amplifier? [May/June 14]

- [Ref .Roy Choudhry, Shail B.Jain, "Linear Integrated Circuits (Second Edition)", Page 178]

- Explain the operation of current to voltage converter 14. (i)

- [Ref .Roy Choudhry, Shail B.Jain, "Linear Integrated Circuits (Fourth Edition)", Page 147] (ii)

- Differentiate between low pass ,high pass ,band pass and band reject filter.Sketch the frequency plot

[Ref .Roy Choudhry, ShailB.Jain, "Linear Integrated Circuits (Fourth Edition)", Page 263]

15. With neat diagram derive the expression for transfer function of a narrow band pass filter and find the resonant frequency factor and Bandwidth

[Ref .Roy Choudhry, ShailB.Jain, "Linear Integrated Circuits (Fourth Edition)", Page 272]

## **UNIT – III-ANALOG MULTIPLIER AND PLL PART-A**

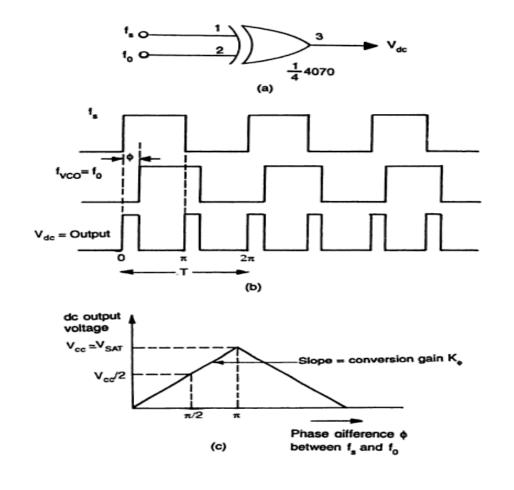

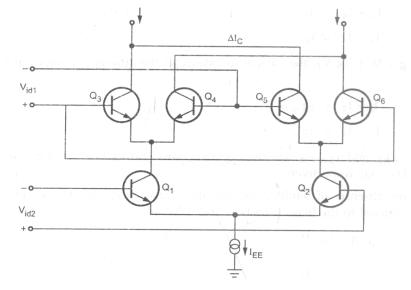

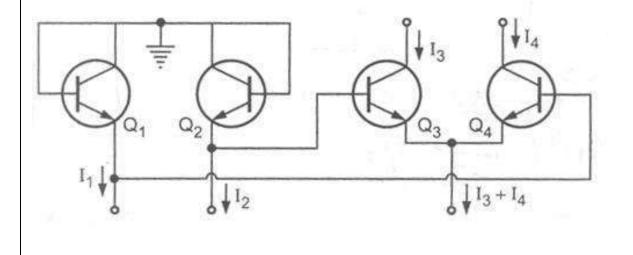

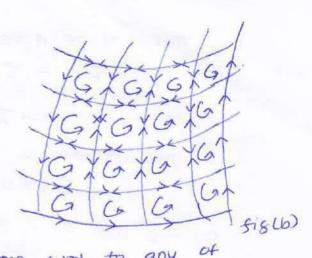

1. What is Gilbert multiplier cell?

## [April/May 2018] [April/May 2019]

A circuit which uses emitter couples pair in series with cross coupled emitter coupled pairs is called Gilbert Cell.

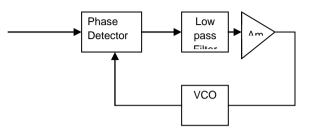

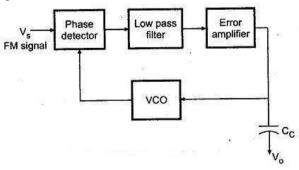

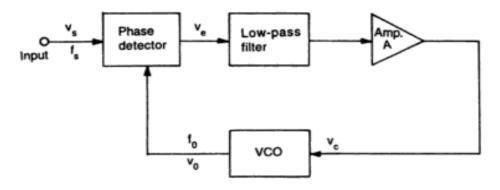

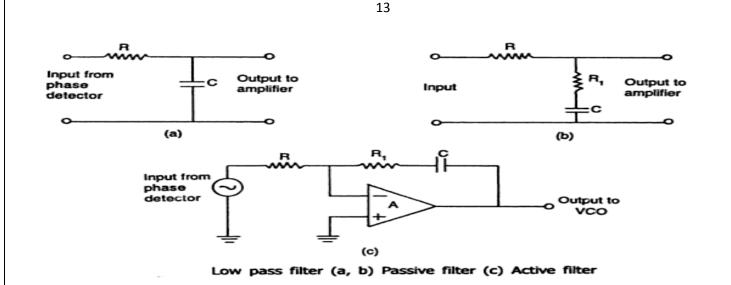

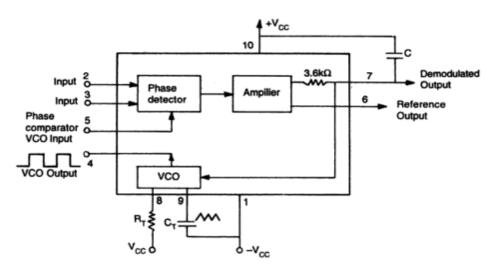

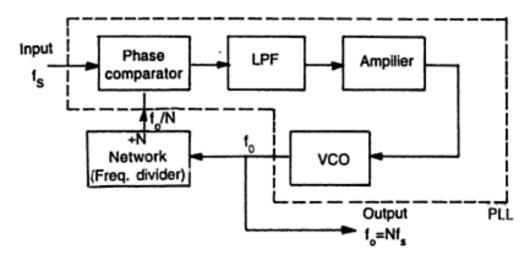

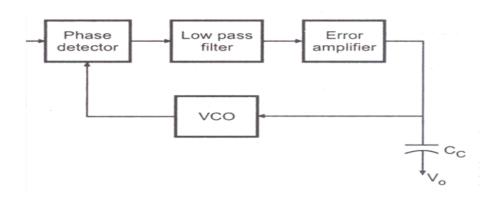

- 2. List the basic building blocks of PLL.

- Phase detector •

- Low pass filter

- Error amplifier

- Voltage controlled Oscillator

- 3. Mention the significance of Gilbert multiplier Cell.

The Gilbert cell mixer or Gilbert cell multiplier is a form of RF mixer circuit that is widely used in integrated circuits. Not only does the Gilbert cell mixer lend itself to integrated circuit technology, but it is able to provide a high level of performance. Gilbert cells are often referred to as four-quadrant multipliers

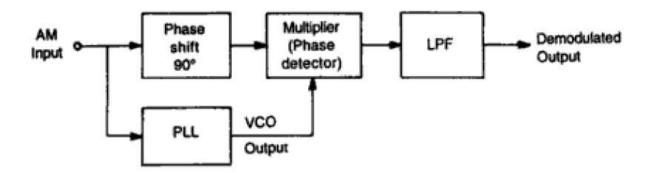

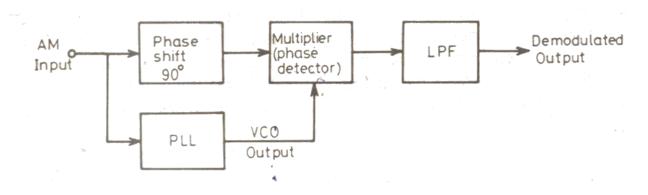

- 4. State various applications of phase locked loop.

- Frequency multiplication and division

- Frequency translation.

- AM detection.

- 4. (a) State any two terminologies associated with multiplier characteristics

- Two Quadrant

- Four Ouadrant

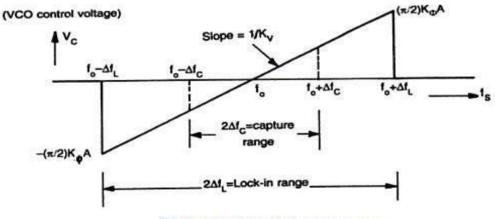

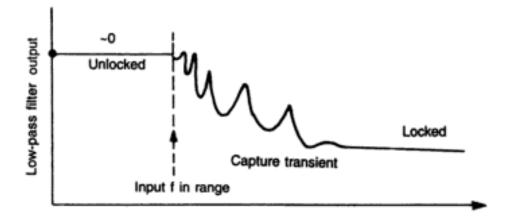

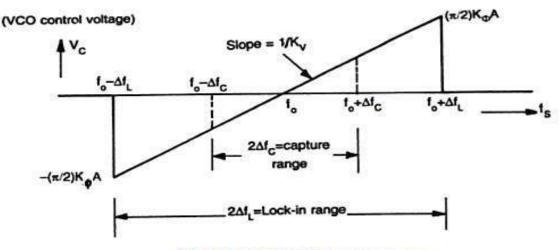

- 5. Define capture range of a PLL?

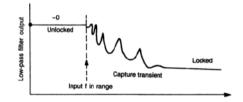

The range of frequency over which the PLL can acquire lock with an input signal is called capture range. The PLL cannot acquire a signal outside the capture range, but once captured, it will hold on till the signal frequency goes beyond the lock-in range, larger capture range is required.

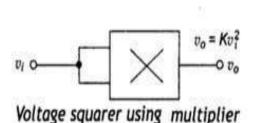

6. How are square root and squarer of a signal obtained with multiplier Circuit ?

## [April/May 2015] [April/May 2017]

Square root circuit using multiplier

7. How is frequency stability obtained in a PLL by use of a VCO?[April/May 2017]

A voltage controlled oscillator is an oscillator circuit in which the frequency of oscillation can be controlled by an externally applied voltage. It provides the linear relationship between the applied voltage and the oscillation frequency.

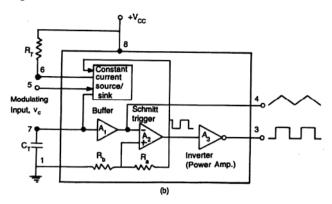

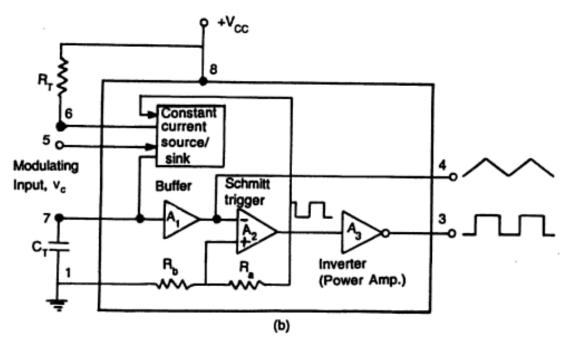

VCO is a free running multivibrator and operates at a set of frequency fo called free running frequency. This frequency is determined by an external timing capacitor and an external resistor. It can also be shifted to either side by applying a dc control voltage Vc to an appropriate terminal of the IC. The frequency deviation is directly proportional to the dc control voltage and hence it is called a "Voltage **Controlled Oscillator**

8. What is a four-quadrant multiplier?

[Nov/Dec 2016]

## [Nov/Dec 2017]

## [Nov/Dec 2018]

[April/May 2018]

[April/May 2019]

[Nov/Dec 2018]

- FM demodulation

It is a multiplier circuit with two inputs being both positive and both negative, then the multiplier is called as four-quadrant multiplier

10. Calculate the lock range and the capture range of the PLL.

Lock in range  $\Delta f_L = +/-7.8 f_o/V$

fois free running frequency

Capture range = +/- =  $[\Delta f_L / (2^* \pi^* R^* C)]^{1/2}$

11. The lock range of a certain general purpose PLL with a free running frequency of 50MHz is specified to be +/- 10% what is its lock range?

Lock in range  $\Delta f_L$ = +/- 7.8 f<sub>o</sub>/ V

- 12. What are the essential building blocks of a PLL?

- The essential building blocks of PLL are

- Phase detector

- Low pass filter

- Amplifier

- Voltage Controlled Oscillator

- 13. What is a two quadrant multiplier?

It is a multiplier one input must be held positive and other can change to positive or negative it is called two quadrant multiplier.

14. What is compander?

The signal is compressed at the transmitter and expanded at the receiver. This is called as companding. The combination of a compressor and expander is called a compander.

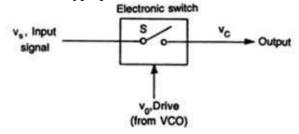

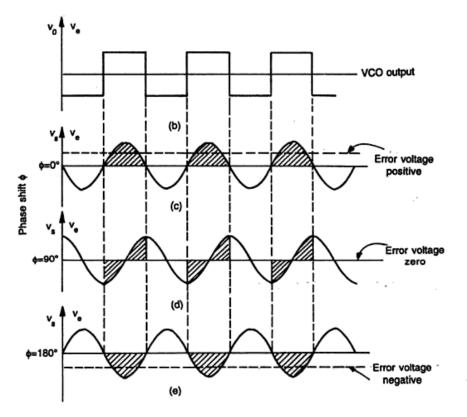

15. State why the phase detector output in a PLL should be followed by a low pass filter?

The phase detector is basically a multiplier and produces the sum  $(f_s+f_o)$  and the difference  $(f_s-f_o)$  components at its output. The high frequency component is removed by the low pass filter and the difference frequency component is applied as control voltage  $v_c$  to VCO.

16. Draw the block diagram of a multiplier using log and antilog amplifiers.

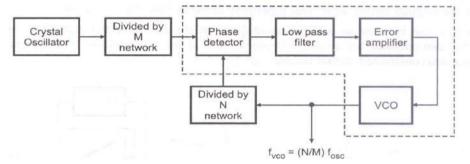

#### 17. What is frequency synthesizer?

Frequency synthesizer is a circuit here each frequency is selected by closing the desired program switches to program a particular frequency output. Period = Tsum + T

18. Define PLL

A phase locked loop is a closed loop system designed to lock the output frequency and phase to the frequency and phase of an input signal

19. Draw the basic block diagram of PLL?

20. What is amplitude modulation?

It is the process of amplitude of carrier wave varies in accordance with the instantaneous value of the amplitude of message signal.

21. Define voltage to frequency conversion factor kv?

$$K_v = \Delta f_o / \Delta v_c$$

Here  $K_{v\,is}$  the modulation voltage required to produce the frequency shift  $\Delta f_o for \; a \; VCO.$

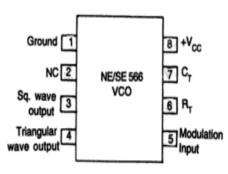

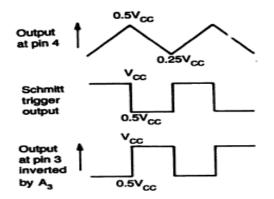

22. What is a voltage-controlled oscillator?

A voltage controlled oscillator is an oscillator circuit in which the frequency of oscillation can be controlled by an externally applied voltage. It provides the linear relationship between the applied voltage and the oscillation frequency.

VCO is a free running multivibrator and operates at a set of frequency fo called free running frequency. This frequency is determined by an external timing capacitor and an external resistor. It can also be shifted to either side by applying a dc control voltage Vc to an appropriate terminal of the IC. The frequency deviation is directly proportional to the dc control voltage and hence it is called a "Voltage Controlled Oscillator".

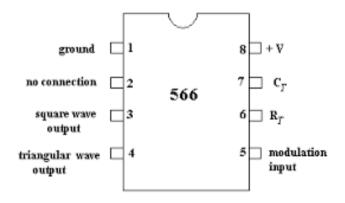

23. Draw the pin diagram of 566 VCO

24. Draw the block diagram of 566 VCO

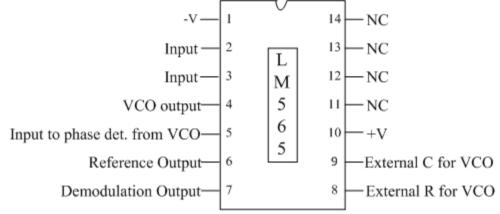

25. Draw the pin diagram of 565 PLL.

26. How VCO different from oscillators?

An oscillator is a circuit that generates the frequency output of fixed frequency. On the other hand a voltage controlled oscillator (VCO) is an oscillator circuit in which the frequency of oscillations can be controlled by an externally applied voltage.

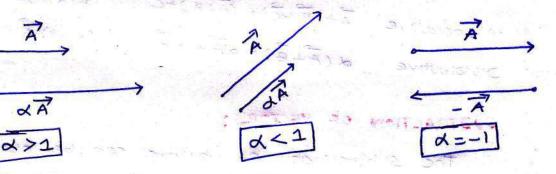

27. When an amplifier is also called an error amplifier?

An amplifier also called an error amplifier in control theory, which accepts the signal  $X_d$  and yields the output signal  $X_0$ =a.Xd, where a is the forward gain of the amplifier is called the open-loop gain of the circuit.

- 28. What are the merits of companding?

- The compression process reduces the dynamic range of the signal before it is transmitted.

- Companding preserves the signal to noise ratio of the original signal and avoids non linear distortion of the signal when the input amplitude is large.

- It also reduces buzz, bias and low level audio tones caused by mild interference.

- 29. List the applications of OTA:

OTA can be used in

- programmable gain voltage amplifier

- sample and hold circuits

- voltage controlled state variable filter

- current controlled relaxation oscillator

- 30. Mention some areas where PLL is widely used.

Radar synchronization

Satellite communication systems

Air borne navigational systems

FM communication systems

31. Define lock-in range of a PLL.

The range of frequencies over which the PLL can maintain lock with the incoming signal is called the lock-in range or tracking range. It is expressed as a percentage of the VCO free running frequency.

32. Define free running mode.

In a PLL if the error control voltage is zero then the PLL is said to be operated in free running mode and its output frequency is called its center frequency  $f_0$ .

33. What are the advantages of variable transconductance technique?

The advantages of variable transconductance technique are:

- 1) Simple to integrate into monolithic chip

- 2) Provides very good accuracy.

- 3) Very cheap hence economical.

- 4) Provides four quadrant operations.

- 5) It provides high speed of operation which is 2 to 3 times more than the logarithmic method.

- 6) Reduced error at least by 10 times.

- 34. With reference to a VCO, define voltage to frequency conversion factor Kv.

Voltage to frequency conversion factor Kv is defind as Kv= $\Delta fo/\Delta vc$

Here  $\Delta vc$  is the modulation voltage required to produce the frequency shift of  $\Delta fo$  for a VCO

35. Draw the relation between the capture ranges and lock range in a PLL.

- 36. Mention two applications of analog multiplier

- Variable-gain amplifier

- Ring modulator

- Product detector

- Frequency mixer

- 37. VCO is called as V-F converter why?

A voltage-controlled oscillator or VCO is an electronic oscillator whose oscillation frequency is controlled by a voltage input ie the change in input voltage results in change in output frequency hence it is called as V-F converter

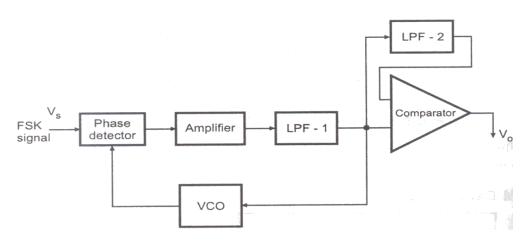

38. Define FSK

Frequency shift keying is a digital modulation technique in which the frequency of carrier signal is varied in accordance with the amplitude of digital modulating signal

39. Draw the block diagram of PLL for FM detection

40. What is the need for frequency synthesizer

A frequency synthesizer is an electronic system for generating any of a range of frequencies from a single fixed time base or oscillator. They are found in many modern devices, including radio receivers, mobile telephones, radiotelephones, walkie-talkies, CB radios, satellite receivers, GPS systems, etc

41. Draw the block diagram of PLL for FSK demodulation

565 As An FSK Demodulator

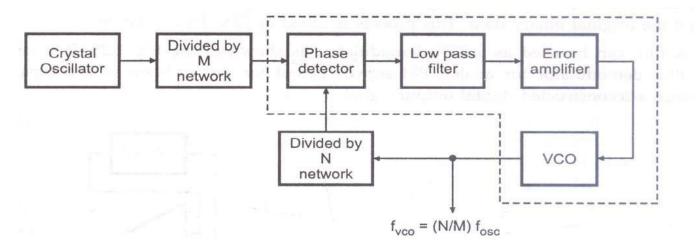

42. Draw the block diagram of PLL for frequency synthesizing

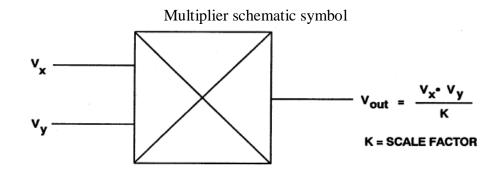

- 43. List the performance parameters of multiplier

- Accuracy

- Linearity

- Bandwidth

- Feed through voltage

- Scale factor

- Quadrant

- 44. State the various techniques used for multiplier.

- Logarithmic summing technique

- Quarter square technique

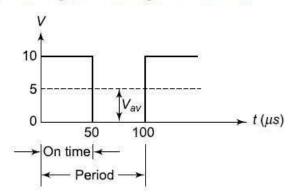

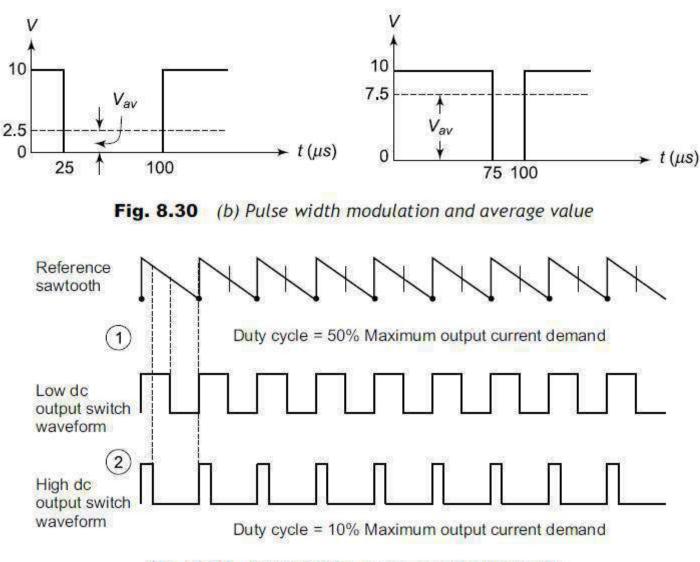

- Pulse width modulation

- Variable transconductance technique

- Triangle averaging technique

- 45. What are the limitations of logarithmic summing technique?

- Poor accuracy

- One quadrant operation

- Temperature instability

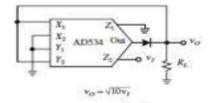

- 46. State the two multiplier ICs

- AD533

- AD534

- 47. Mention the applications of AD533

- Function generator

- Peak detection

- RMS computation

- Phase detection

- Automatic gain control

- Square and square root extractor

- 48. Mention the applications of AD534

- Multiplier

- Divider

- High quality analog signal processing

- Square and square root extractor

- Differential ratio and percentage computation

- Accurate voltage controlled oscillators and filters

- 49. What is pull in time?

From the application of the input signal ,the total time taken by the PLL to establish a lock is called pull in time.

- 50. Which parameter decides the pull in time

- Initial Frequency and phase difference between two signals

- Overall loop gain

- Bandwidth of low pass filter.

- 51. Draw the relation between the capture range and lock range of PLL

PLL lock-in range and capture range

## PART-B&C

1. (i) Explain in detail the operation of a basic phase locked loop.(5)

## [Nov/Dec 2018]

[Ref .Roy Choudhry, ShailB.Jain, "Linear Integrated Circuits (Fourth Edition)", Page 327]

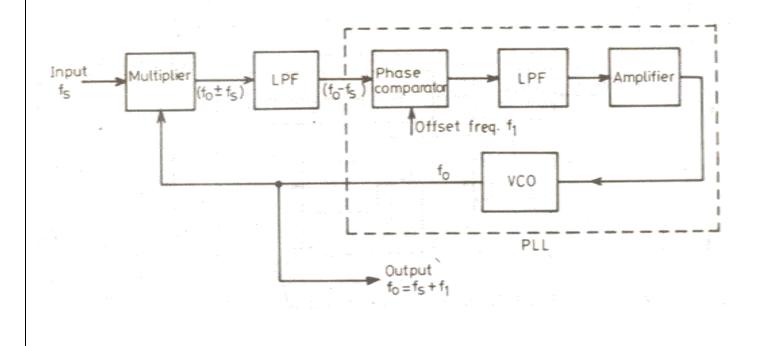

(ii) How are PLLs applied for frequency synthesizing and FM detection.(8)

## [Nov/Dec 2018]

Ref .Roy Choudhry, ShailB.Jain, "Linear Integrated Circuits (Fourth Edition)", Page 343]

A PLL has a free running frequency of 400 kHz and the band width of the low pass filter is 8kHz.Will the loop tend to acquire lock for an input signal of 550 kHz? Explain in this case ,assume that the phase detector produces sum and difference frequency components. [Nov/Dec 2018] [Nov/Dec 2017]

| Ire            | luency components. [Nov/Dec 20                                                                        | 18] [Nov/Dec 2017]                      |

|----------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------|

| 3. (i)         | Obtain the expression for free running frequency of voltag                                            | e controlled                            |

|                | oscillator.(6)                                                                                        | [Nov/Dec 2018]                          |

| נן             | ef .Roy Choudhry, ShailB.Jain, "Linear Integrated Circuits (Fourth Edition                            | n)", Page 334]                          |

| (ii)           | Design an analog multiplier employing an emitter coupled                                              | transistor                              |

|                | pair. (7)                                                                                             | [Nov/Dec 2018]                          |

| ſ              | ef .Roy Choudhry, ShailB.Jain, "Linear Integrated Circuits (Fourth Edition                            |                                         |

| _              | cuss briefly about analog multiplier ICs                                                              | [April/May 2018]                        |

|                | 7. Roy Choudhry, ShailB.Jain, "Linear Integrated Circuits (Fourth Edition)"                           |                                         |

|                | cuss in detail about VCO using suitable diagram.                                                      | [April/May 2018]                        |

|                | F.Roy Choudhry, ShailB.Jain, "Linear Integrated Circuits (Fourth Edition)"                            |                                         |

| [              |                                                                                                       | , 8 ]                                   |

| 6. Wi          | h neat diagram explain the design of (i) Frequency Synthe                                             | sizer (ii) Frequency                    |

|                | ision circuit using PLL IC 565                                                                        | [April/May 2017]                        |

| DI             | [Ref .Roy Choudhry, ShailB.Jain, "Linear Integrated Circuits (Fourth Edit                             | - 1                                     |

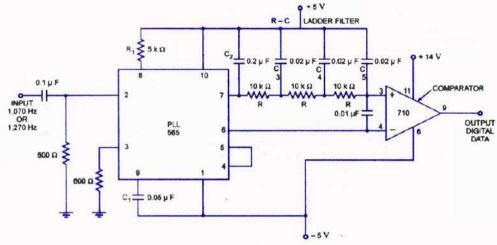

| 7. (i)         | Discuss the principle of operation of NE 565 PLL circuit                                              |                                         |

| 7. (I)         | [Ref .Roy Choudhry, ShailB.Jain, "Linear Integrated Circuits (Fourth                                  |                                         |

|                | (ii) How can PLL be modeled as a frequency multiplier?                                                | [Nov/Dec 2016]                          |

|                | [Ref .Roy Choudhry, ShailB.Jain, "Linear Integrated Circuits (Fourth                                  |                                         |

| 8. Ex          | blain the Application of PLL as AM detection,FM detection an                                          | , · · · ·                               |

|                | nodulation                                                                                            | [April/May 2016]                        |

| aei            | [Ref .Roy Choudhry, Shail B.Jain, "Linear Integrated Circuits (Second                                 |                                         |

| 9. Ex          | plain the basic blocks of PLL and determine expressions for lo                                        |                                         |

| cap            | ture range                                                                                            | [April/May 2015]                        |

|                | [Ref .Roy Choudhry, Shail B.Jain, "Linear Integrated Circuits (Second                                 | d Edition)", Page 353&                  |

| 370<br>10 i) I |                                                                                                       | vinla of Operational                    |

|                | Vith neat simplified internal diagram explain the working princ nsconductance Amplifier(OTA)          | [April/May2015]                         |

| 110            | [Ref .Roy Choudhry, Shail B.Jain, "Linear Integrated Circuits (Second                                 |                                         |

| ii)            | Explain the application of VCO for FM generation                                                      | [April /May15]                          |

| ,              | [Ref .Roy Choudhry, Shail B.Jain, "Linear Integrated Circuits (Second                                 | d Edition)", Page 225]                  |

| 11. Wi         | h suitable block diagram explain the operation of 566 voltage                                         | controlled oscillator.                  |

| Als            | o derive an expression for the frequency of the output wavefor                                        |                                         |

| 10 F           | [Ref .Roy Choudhry, Shail B.Jain, "Linear Integrated Circuits (Second                                 |                                         |

|                | blain the working principle of four quadrant variable form trans                                      |                                         |

|                | tiplier<br>ef .Roy Choudhry, Shail B.Jain, "Linear Integrated Circuits (Second Editio                 | [May/June 2016]                         |

| -              | w the analog multiplier IC and explain its features and Explain                                       | . –                                     |

|                | log multiplier IC                                                                                     | [April/May 2015]                        |

|                | [Ref .Roy Choudhry, Shail B.Jain, "Linear Integrated Circuits (Seco                                   |                                         |

|                | xplain Analog Multiplier using Emitter Coupled Transistor Pai                                         |                                         |

|                | ef .Roy Choudhry, Shail B.Jain, "Linear Integrated Circuits (Second Editio                            | on)", Page 183]                         |

| 11)            | Explain Gilbert Multiplier cell in detail                                                             | 1 E 1'4' \V D 1021                      |

| 15 Ev          | [Ref .Roy Choudhry, Shail B.Jain, "Linear Integrated Circuits (Secondarian the application of PLL for | id Edition)", Page 183]                 |

| 1 <b>J.</b> ĽX | blain the application of PLL for<br>i. Frequency synthesizing                                         |                                         |

|                | ii. Clock synchronization                                                                             |                                         |

| ſRe            | Roy Choudhry, Shail B.Jain, "Linear Integrated Circuits (Second Edition                               | )", Page 3421                           |

| Lice           |                                                                                                       | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |

## UNIT -IV - ANALOG TO DIGITAL AND DIGITAL TO ANALOG CONVERTERS

## PART A:

1. Define settling time

[April/May 2019] It is the time the converter takes for the output to settle within a specified band

+/-(1/2)LSB 2. What is the largest value of output voltage from an 8 bit DAC that produces 1.0V for a digital input of 00110010 [April/May 2019]

5.10V

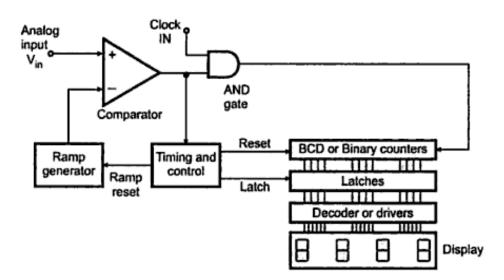

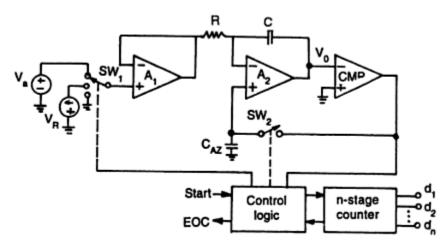

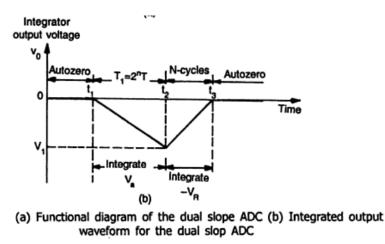

3. Differentiate between direct type and integrating type in ADC converters.

[Nov/Dec 2018]

Direct type ADCs compare a given analog signal with the internally generated equivalent signal.

Integrating type ADCs perform conversion in an indirect manner by first changing the analog input signal to linear function of time or frequency and then to a digital code.

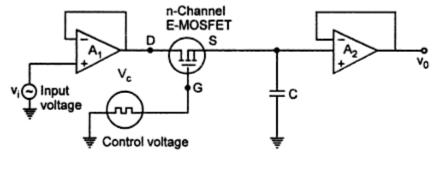

4. What is the need of sample and hold circuit. [Nov/Dec 20178]

For accurate analog and digital conversion the analog input voltage should be held constant during the conversion cycle. The input voltage is kept constant during conversion time using sample and hold circuit.

5. Define Sampling.

The process of converting analog signals into discrete time signals is called sampling.

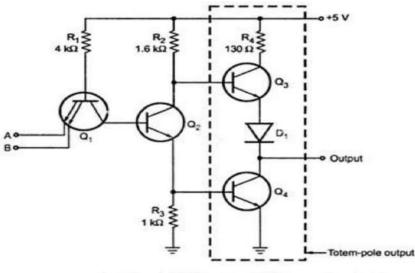

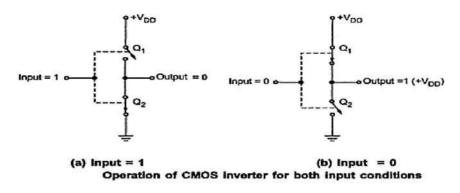

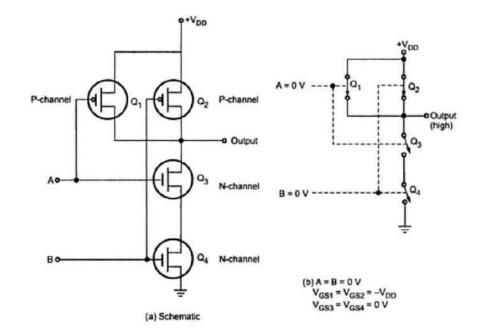

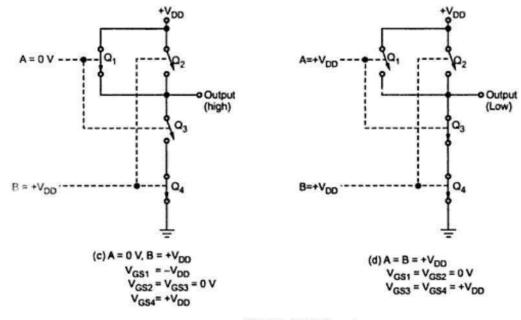

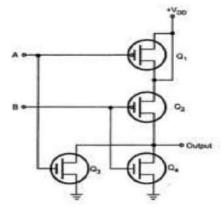

- 6. Write the name of the switches used in MOS transistors. [April/May 2018]

- Totem pole MOSFET switch

- CMOS inverter switch

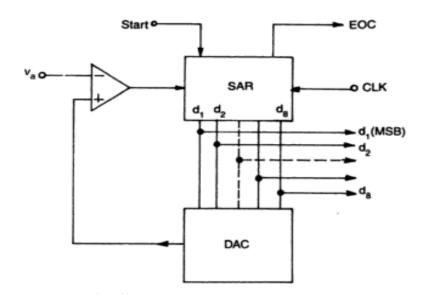

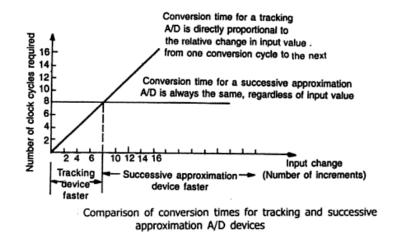

- 7. How is the classification of A/D converters carried out based on their operational features? [Nov/Dec 2017]

- A/D converter are classified into two groups according to their conversion

- Direct type ADC (i)

- (ii) Integrating type ADC

- Direct Type ADC

- Flash Type converter (i)

- (ii) Counter type converter

- (iii) Tracking or servo converter

- (iv) Successive approximation type converter

Integrating type ADC

- Charge balancing ADC (i)

- (ii) Dual slope ADC

- 8. Find the number of resistors required for an 8 bit weighted resistor D/A converter. Consider the smallest resistance is R and obtain those resistance values.

[Nov/Dec 2017]

The No of Resistors required =8

The resistance values are  $2^{1}R, 2^{2}R, 2^{3}R, 2^{4}R, 2^{5}R, 2^{6}R, 2^{7}R, 2^{8}R$

## [April/May 2018]

9. Why are Scottky diodes used in sample and hold circuits? [April/May 2017]

Schottky diodes can be used in diode-bridge based sample and hold circuits. When compared to regular p-n junction based diode bridges, Schottky diodes can offer advantages. A forward-biased Schottky diode does not have any minority carrier charge storage. This allows them to switch more quickly than regular diodes, resulting in lower transition time from the sample to the hold step. The absence of minority carrier charge storage also results in a lower hold step or sampling error, resulting in a more accurate sample at the output

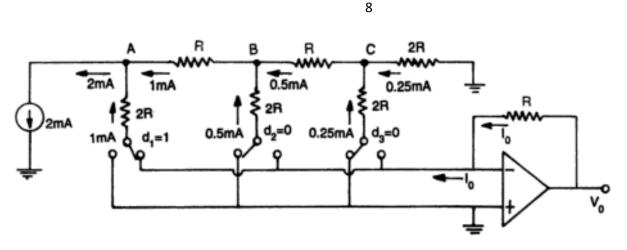

10. What are the advantages of inverted R-2R (current type) ladder D/A converter over R-2R (voltage type) D/A converter? [Nov/Dec 2016]

In R-2R ladder type DAC current flowing in the resistors changes as the input data changes. More power dissipation causes heating which in turn creates non-linearity in DAC. This problem can be avoided in inverted R-2R ladder type as the current divides equally at each node.

11. What is the need for electronic switches in D/A converter? [Nov/Dec 2016]

The Switches which connects the digital binary input to the nodes of a D/A converter is an electronic switch

12. A 12 bit D/A converter has a resolution of 20mv/LSB.Find the full scale output voltage. [May/June 2016]

Re solution =

$$\frac{V_{oFS}}{2^n - 1}$$

Where,  $V_{oFS}$  is the full scale output voltage

n is the number of bits

$$V_{oFS} = \text{Re solution} * (2^{n} - 1)$$

$V_{oFS} = 20 * 10^{-3} * (2^{12} - 1)$

$V_{oFS} = 81.9V$

13. Draw the binary ladder network of DAC, If the value of the smaller resistance is 10K.What is the value of other resistance? [May/June 2016]

The value of other resistance=2R=20 Kohm

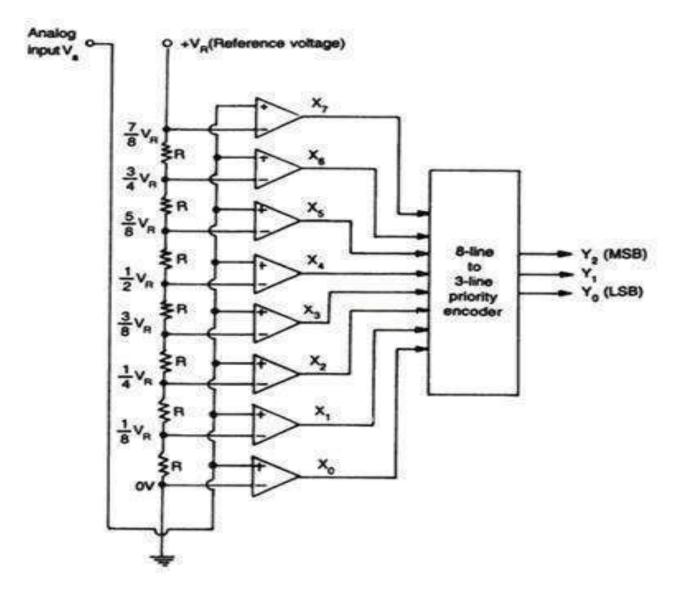

14. Determine the number of comparators and resistors required for 8 bit flash type ADC [Nov/Dec2015]

No Of comparators required is  $=2^8-1=255$

- 15. Mention two advantages of R-2R ladder type DAC when compared to weighted resistor type DAC [Nov/Dec 2015]

- Only two resistor values are used in R-2R ladder type.

- It does not need as precision resistors as Binary weighted DACs.

- It is cheap and easy to manufacture.

- 16. What would be produced by a DAC whose output ranges is 0 to 10V and whose input binary number is 10111100(for a 8 bit DAC)? [April/May 2015]

$$V_{o} = 10V(1x(1/2)+0x(1/2)^{2}+1x(1/2)^{3}+1x(1/2)^{4}+1x(1/2)^{5}+1x(1/2)^{6}+0x(1/2)^{7}+0x(1/2)^{8})$$

V<sub>o</sub>=7.34V

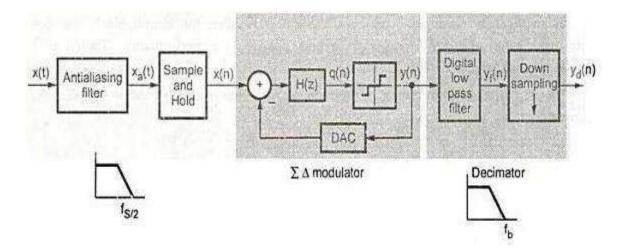

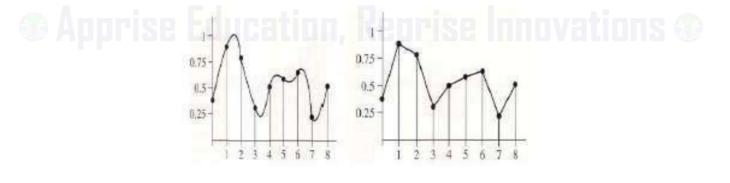

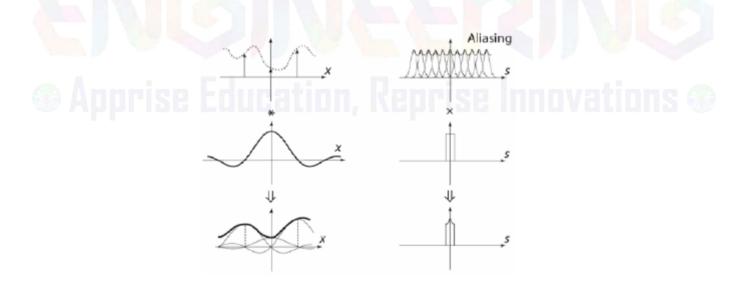

**17.** What is over sampling?

## [April/May 2015]

The technique of increasing the apparent sampling frequency of a digital signal by repeating each digit a number of times, in order to facilitate the subsequent filtering of unwanted noise.

In signal processing, oversampling is the process of sampling a signal with a sampling frequency significantly higher than the Nyquist rate. Theoretically a bandwidth-limited signal can be perfectly reconstructed if sampled above the Nyquist rate, which is twice the highest frequency in the signal. Oversampling improves resolution, reduces noise and helps avoid aliasing and phase distortion by relaxing anti-aliasing filter performance requirements.

18. State the reason for keeping the integrating time in the dual slope analog to digital converter equal to that of mains supply period.

The dual slope ADC integrates the input signal for a fixed time, hence it provides excellent noise rejection of ac signals whose periods are integral multiples of the integration time Ti. Thus as noise superimposed on the input signal such as 50Hz power link pick-up will be averaged during the input integration time. So choose clock period T, so that  $2^{n}$ T is an exact integral multiple of the line period (1/50) second = 20 ms.

19. Which is the fastest A/D converter? Give reason.

Parallel comparator A/D is the fastest and most expansive comparator.

Because it consists of a resistive divider network, 8 op-amp comparators and a 8 line to 3 line encoder.

20. A 12 bit D/A converter have resolution of 30 mV/ LSB. Find the full scale output voltage.

$$Vo = Vfs/2$$

Vfs = 2xVo

= 2x30 = 60 mv.

21. Calculate the number of comparators required for realizing a 4 bit flash A/D converter.

Numbers of comparators required are

$$2^n - 1$$

$2^4 - 1 = 16 - 1 = 15$ .

22. Draw a sample and hold circuit.

23. Define resolution of a D/A converter?

The resolution of a DAC is defined as the smallest change in voltage, which may be produced at the output or input of the converter.

- 24. How many comparators are required to build n –bit flash type A/D converter? Comparator required to build n –bit flash type A/D converter is 2<sup>n</sup> – 1 Where n is the desired number of bits.

- 25. Define monotonicity with respect to D/A converter?

A DAC is said to be monotonic if the analog output increases or remains the same as the digital input increases. This results in the output always being single – valued.

26. Why is R-2R ladder network DAC better than weighted resistor DAC?

Wide ranges of resistors are required in binary weighted resistor type DAC.

- This can be avoided by using R-2R ladder type DAC.

- i. Easier to build accurately as only two precision metal film resistors are required.

- ii. Number of bits can be expanded by adding more sections of same R-2R values.

- iii. In inverted R-2R ladder DAC, node voltages remain constant with changing input binary words. This avoids any slowdown effects by stray capacitances.

- 27. Which type of ADC is used in all digital voltmeter?

Dual slope ADC converters are particularly suitable for accurate measurement of slowly varying signals, such as digital panel meters and multimeters.

28. What do you mean by delta modulation?

Delta modulation is a method of information transmission with the help of pulses. It is one type of digital modulation and it determines the increase or decrease of the signal sample with respect to previous sample. And encodes this rise or fall of amplitude by 1 bit.

- 29. List the application of sample and Hold circuits?

- i. It is used in ADC.

- ii. It is used in digital interfacing

- iii. It is used in pulse modulation system

- iv. It is used in analog demultiplexer

- 30. Mention the types of DAC techniques?

- ii. Weighted resistance

- iii. Inverted R-2R ladder

- iv. Multiplying.

- 31. Define the resolution of DAC?

Resolution of DAC is defined as the change in the output voltage

corresponding to the change of one bit in the digital input.

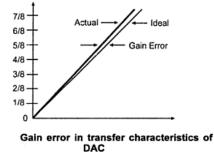

32. Explain in brief stability of a converter:

The performance of converter changes with temperature age & power supply variation. So all the relevant parameters such as offset, gain, linearity error& monotonicity must be specified over the full temperature & power supply ranges to have better stability performances.

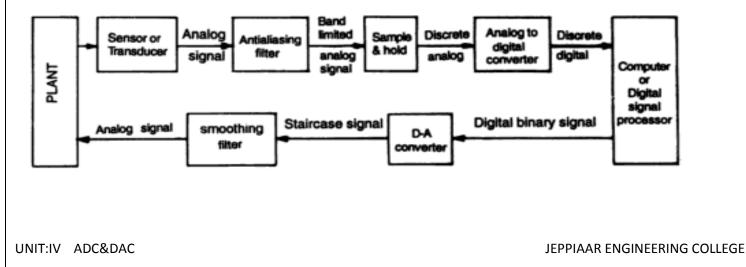

33. What is meant by linearity?

The linearity of an ADC/DAC is an important measure of its accuracy & tells us how close the converter output is to its ideal transfer characteristics. The linearity error is usually expressed as a fraction of LSB increment or percentage of full-scale voltage. A good converter exhibits a linearity error of less than  $\pm \frac{1}{2}$ LSB.

34. What is monotonic DAC?

A monotonic DAC is one whose analog output increases for an increase in digital input.

35. What is multiplying DAC?

A digital to analog converter which uses a varying reference voltage VR is called a multiplying DAC (MDAC). If the reference voltage of a DAC, VR is a sine wave given by:

$$V(t) = V_{in} \cos 2\pi ft;$$

Then,  $V_o(t) = V_{om} \cos (2\pi f t + 180^{\circ})$

36. What is a sample and hold circuit? Where it is used?

A sample and hold circuit is one which samples an input signal and holds on to its last sampled value until the input is sampled again. This circuit is mainly used in digital interfacing, analog to digital systems, and pulse code modulation systems. 37. Define sample period and hold period.

The time during which the voltage across the capacitor in sample and hold circuit is equal to the input voltage is called sample period. The time period during which the voltage across the capacitor is held constant is called hold period.

- 38. Define accuracy of converter.

- Absolute accuracy:

It is the maximum deviation between the actual converter output & the ideal converter output.

Relative accuracy:

It is the maximum deviation after gain & offset errors have been removed. The accuracy of a converter is also specified in form of LSB increments or % of full scale voltage.

39. What output voltage would be produced by a D/A converter whose output range is 0 to 10 V and whose input binary number is 0110 for a 4 bit DAC.

$$\text{Given}V_{o FS} = 10V$$

$$Resolution = \frac{10}{10^4 - 1} = 0.6667 \, V$$

The output voltage at 0110=0.6667\*6=4V

40. What is the main drawback of dual slope ADC?

The conversion time of dual slope ADC is high .This is the main drawback of

[April/May 16]

dual slope ADC.

- 41. Draw the binary ladder network of DAC .If the value of the smaller resistance is 10K what is the value of the other resistance

- 42. A 12 bit D/A converter has resolution of 20mV/LSB.Find the full scale output voltage

Given resolution = 20mV/LSB

Full scale output voltage =Resolution $(10^{12}-1)=20*10^{-3}(10^{12}-1)$ 43. Draw the weighted resistor network of DAC[APRIL/MAY 16]

44. Draw the functional diagram of the successive approximation ADC

44. Define voltage droop.

The leakage current causes voltage of the capacitor to drop down. This is referred to as droop.

45. What are current driven DACs?

The DAC in which the problem of radioed emitter is solved by using equal value current sinks and exploiting the current scaling capability of the inverter R-2R ladder to obtain binary weighted contributions to the output is known as current driven DAC

- 46. What are the specifications of D/A converter?

- Accuracy

- Resolution

- Offset

- Linearity error

- Conversion time

- Monotonicity

- 47. Define conversion time of DAC

It is the time required for conversion of analog signal into its digital equivalent.

48. What is linear error?

The linear error is defined as the amount by which the actual output differs from ideal straight line output characteristics of DAC

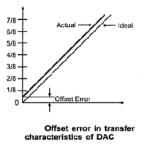

49. Define Offset error.

Offset error is defined as the nonzero level of the output voltage when all inputs are zero.

50. Compare single slope ADC and dual slope ADC

| Sl.No | Single slope ADC        | Dual slope ADC          |

|-------|-------------------------|-------------------------|

| 1.    | Resolution is low       | Resolution is high      |

| 2.    | Does not use integrator | It uses integrator      |

| 3.    | Accuracy is low         | Accuracy is high        |

| 4.    | Less immune to          | More immune to          |

|       | temperature variations  | temperature variations  |

| 5.    | More sensitive to input | Less sensitive to input |

|       | voltage variations      | voltage variations      |

## PART-B&C

| 1.                                                                           | (i)  | (i) Describe the operational feature of R-2R ladder type D/A converter.(7) |                              |

|------------------------------------------------------------------------------|------|----------------------------------------------------------------------------|------------------------------|

|                                                                              |      |                                                                            | [Nov/Dec2018]                |

|                                                                              |      | [Ref .Roy Choudhry, ShailB.Jain, "Linear Integrated Circuits (F            | Fourth Edition)", Page 352]  |

|                                                                              | (ii) | Discuss various switches employed for D/A converter                        | rs.(6) [Nov/Dec2018]         |

|                                                                              |      | [Ref .Roy Choudhry, ShailB.Jain, "Linear Integrated Circuits               | (Fourth Edition)", Page 351] |

| 2. (i) With a neat block diagram, explain the operation of flash and success |      | lash and successive                                                        |                              |

|                                                                              |      | approximation type A/D converter. (10)                                     | [Nov/Dec2018]                |

|                                                                              |      | [Ref .Roy Choudhry, ShailB.Jain, "Linear Integrated Circuits (F            | ourth Edition)", Page 358]   |

|                                                                              | (ii) | What is oversampling? Give examples of oversampling                        | ng converter. (3)            |

|                                                                              |      |                                                                            | [Nov/Dec2018]                |

| 3.                                                                           | (i)  | For a 4 bit R-2R ladder D/A converter assume that the                      | e full scale voltage is      |

|                                                                              |      | 16V.Calculate the step change in output voltage on in                      | put varying from 0111 to     |

|                                                                              |      | 1111(8)                                                                    | [Nov/Dec2018]                |

|                                                                              |      | [Ref .Roy Choudhry, ShailB.Jain, "Linear Integrated Circuits (Fou          | rth Edition)", Page 357]     |